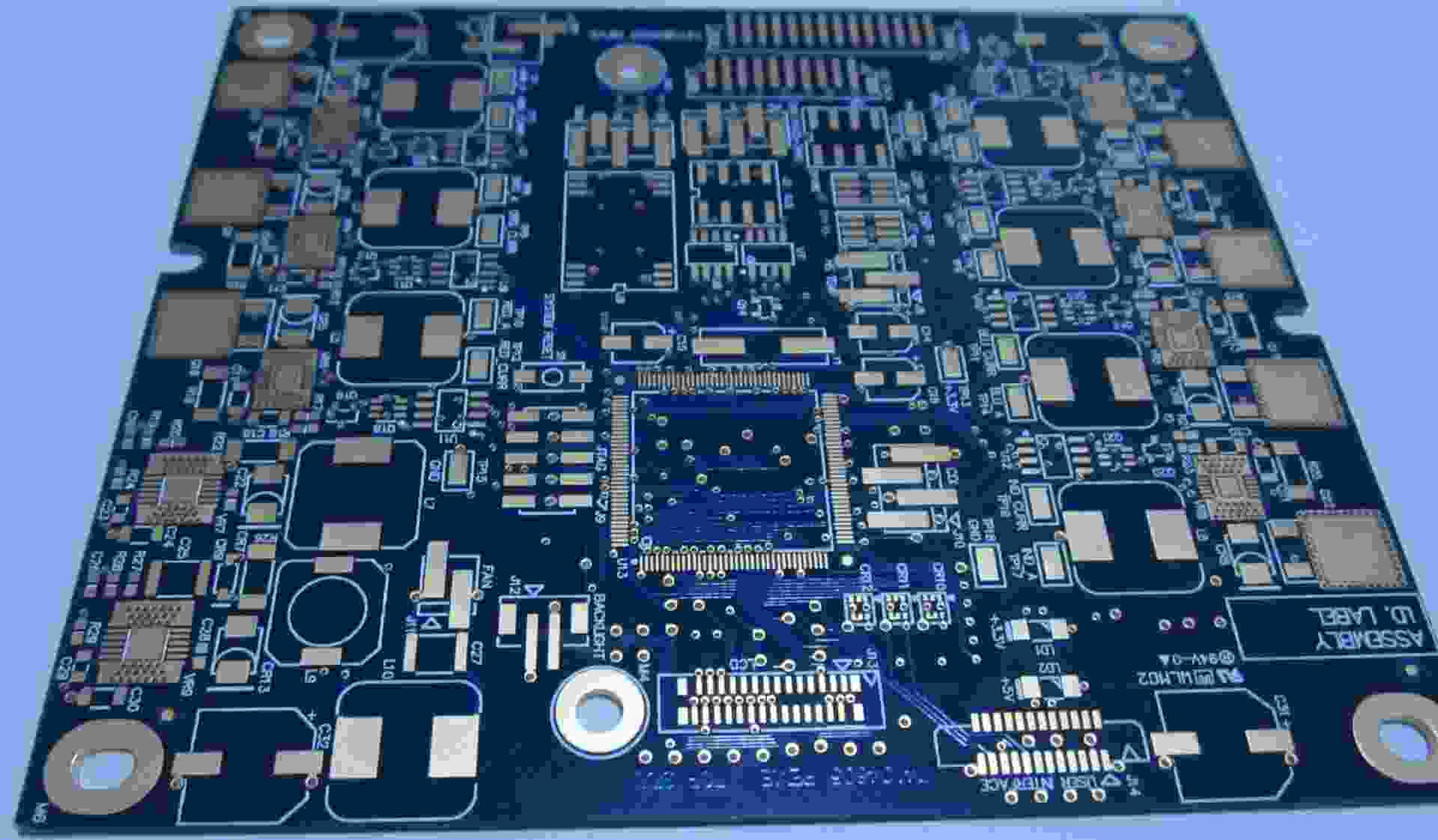

PCBのクロス分割設計の説明と分析

回路設計では、48V、12V - 12V、5V、 - 5V、3.3V、2.5V、1.8V、1.5V、およびその他の一般的なタイプの電源など、PCB 上に複数の電源と複数のグランドがますます増えています。 AGND (アナログ グランド)、DGND (デジタル グランド)、PGND (保護グランド) およびその他のさまざまな機能。 一部の IC では、IC が一点接地を行うことを明示的に要求し、必要な電源とグランド プレーンがくり抜かれています。 これらのグランドや電源の高い信頼性を確保するために、各電源やグランドを層、つまりプレーンに分散させることは、必然的に回路基板の層数の増加につながり、回路基板の製造コストが高くなります。 大幅に増加します。 前述のように、回路基板の製造コストは層の数に比例します。 コストを節約し、回路基板の信頼性を確保するために、エンジニアは回路基板の特性に応じて、同じプレーン上に 2 つ以上の PCB の電源またはグランドを設計し、その結果、電源プレーンとグランド プレーンが不完全になります。 グランド(電源)層のセグメンテーション。

1、PCB基板のクロス分割設計

回路上の PCB 配線はグランド (電源) 層を介して分割され、信号の完全性に大きな影響を与えるだけでなく、回路の EMI および EMC 特性も変化します。 これが横割り問題です。 これらは、電子技術者が簡単に無視できる問題でもあります。 分野横断的なトピックには、主に次の 2 つの情報源があります。

1. 電源/グランドプレーンの分割

同じレイヤー(層)には、アナログ部門とデジタル部門があります。 PCB ルーティングがこのパーティション バンドを通過すると、クロス パーティションの問題が発生します。

2. 密集したビアまたは密集して挿入された (圧着された) デバイスのピンの不適切な定義によるセグメンテーション

ピンの定義中に高密度のビアまたは高密度のプラグイン (圧着) デバイスが不当に分散され、ピン間の間隔が非常に小さい場合、層または定義層に狭い分離ゾーンが作成されます。 この分断に配線を通すと交差分断が発生します。

これらの配線方法は表面上非の打ちどころがなく、すっきりと美しく、一般の電子または回路技術者の好ましい配線方法でもあります。 これらのビアの対応する領域の電源/グランド プレーンを見ると、電源と層のセグメンテーションの問題が発生することがわかります。

ビアの間隔が狭いため、電源/グランド プレーンに長い分割ストリップが作成されます。 このパーティション バンドを通るケーブルがある場合、クロス パーティションの問題も発生します。 この種の問題は、主に回路内のバス配線に現れ、エンジニアの注意を喚起する必要があります。

同様に、ビア (パッドとビアを含む) がグランド/電源プレーンを通過する場合、ビア間の間隔が近すぎると、上記の問題も発生します。 この種の問題は、主に密集した (圧着された) デバイスのピンの定義が正しくない場合に発生します。 したがって、密集した (圧着された) デバイスのピン信号を定義する場合は、信号の数と種類だけでなく、信号バスの配置も考慮する必要があります。 グランドプレーン。

2、 PCBクロススプリット配線の危険性

クロス スプリット ルーティングの主な危険性は次のとおりです。

(1) 配線のインピーダンス不連続。

(2) 信号間のクロストークが発生しやすい。

(3) 信号の反射を引き起こす可能性があります。

(4) 出力波形が容易に発振できるように、電流ループの面積とインダクタンスを大きくします。

(5) 宇宙への放射干渉を増大させ、宇宙磁場の影響を受けやすい。

(6) ボード上の他の回路との磁界結合の可能性を高めます。

(7) ループ インダクタンスでの高周波電圧降下は、コモン モード放射源を形成し、外部ケーブルを介してコモン モード放射を生成します。

厳密なインピーダンス制御を必要とし、ストリップライン モデルに従ってルーティングされる高速信号ラインの場合、上部プレーン、下部プレーン、または上下プレーンのノッチもストリップライン モデルを破壊し、インピーダンスの不連続を引き起こし、深刻な信号歪みを引き起こします。 、信号の信頼性を低下させます。

電磁干渉に対するクロス スプリット ルーティングの影響を鮮明に説明するために、著者は実験的な比較を行いました。 比較結果からクロスセグメンテーションの影響を簡単に確認できます。 PCBA メーカーは、PCB クロス分割設計、説明と分析、電源/グランド プレーン分割、および PCB クロス分割ルーティングの危険性について説明します。