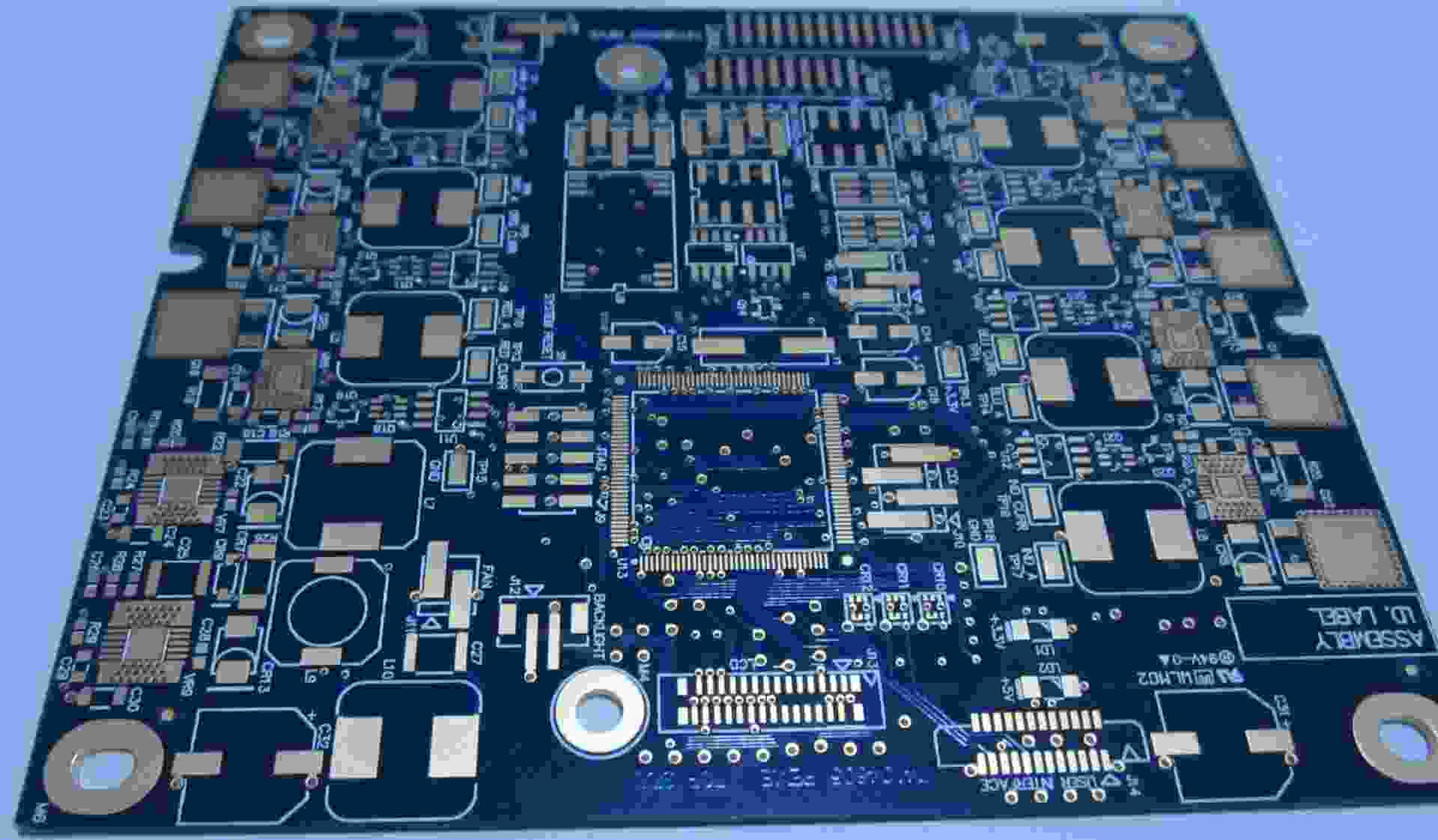

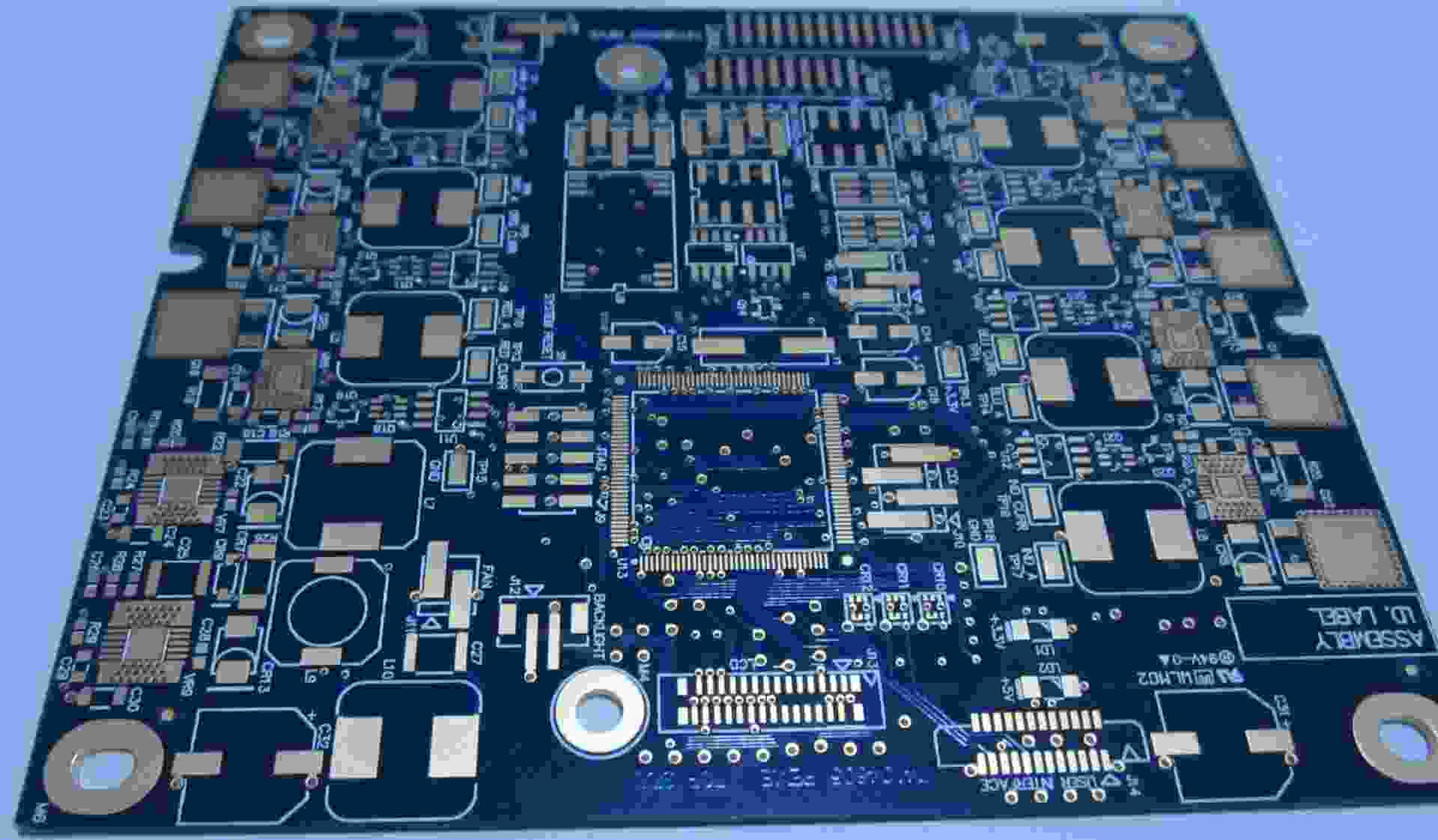

Pcb factory: ケイデンスに基づく高速 PCB 設計共有

1 はじめに

通信に対する人々の要求の継続的な改善に伴い、信号の伝送と処理の速度はますます高速化する必要があります。 対応する高速PCBもますます広く使用されており、設計はますます複雑になっています。高速回路には2つの意味があります。1つは高周波です。 一般に、デジタル回路の周波数は 45MHz から 50MHz に達するか、それを超えると考えられており、この周波数で動作する回路はシステム全体の 3 分の 1 を占めており、高速回路と呼ばれています。 信号の立ち上がり時間が信号伝送遅延の 6 倍未満の場合、信号は高速信号と見なされ、信号の特定の周波数とは無関係に考慮されます。

2 高速基板設計の基本内容

現代の回路設計における高速回路設計の割合はますます大きくなり、設計の難易度はますます高くなっています。 その解決には、高速デバイスだけでなく、設計者の知恵と慎重な作業が必要です。 既存の高速回路の問題を解決するには、特定の状況を注意深く調査および分析する必要があります。一般的に言えば、主に3つの側面が含まれます。シグナルインテグリティ設計、電磁両立性設計、およびパワーインテグリティ設計です。

2.1 シグナルインテグリティ設計

シグナル インテグリティは、信号ライン上の信号の品質を指します シグナル インテグリティが良好な信号とは、必要なときに必要な電圧レベル値を備えていることを意味します シグナル インテグリティが低いのは、単一の要因ではなく、ボード レベルの設計における複数の要因によって引き起こされます 特に 高速回路では、使用されるチップのスイッチング速度が速すぎ、端子コンポーネントのレイアウトが不合理であり、回路の相互接続が不合理であり、信号の完全性の問題が発生します。 具体的には、クロストーク、反射、オーバーシュートとアンダーシュート、発振、信号遅延などを含みます。

2.1.1 クロストーク

クロストークは、隣接する 2 つの信号線間の不要なカップリングです。 信号ライン間の相互インダクタンスと相互容量は、ラインにノイズを発生させます。 したがって、それはまた、誘導性クロストークと容量性クロストークに分けられ、それぞれ結合電流と結合電圧を引き起こします。 信号のエッジ レートが 1ns 未満の場合、クロストークを考慮する必要があります。信号線に交流信号電流が流れると、交番磁界が発生し、隣接する信号線によって信号電圧が誘起されます。 一般に、PCB レイヤーのパラメーター、信号線間の距離、ドライバーとレシーバーの電気的特性、および信号線の終端モードは、クロストークに一定の影響を与えます。ケイデンスの信号シミュレーション ツールでは、6 つの結合された信号線を 同時にクロストーク後にシミュレートされます。 設定できるスキャン パラメータには、PCB の誘電率、媒体の厚さ、銅蒸着の厚さ、信号線の長さと幅、および信号線の間隔が含まれます。シミュレーション中に、損傷した信号線も指定する必要があります。 このライン上の他の信号ラインの干渉を調査します。 励磁を一定高または一定低に設定し、この信号線上の他の信号線の誘起電圧の合計を測定できるようにして、要件を満たす最小間隔と最大並列長を取得できるようにします。

2.1.2 リフレクション

反射は、光が不連続な媒体を通過するときに私たちが知っていることと同じで、エネルギーを反射します。つまり、伝送ライン上の信号のエコーです。 このとき、信号電力は負荷に完全には伝達されず、一部が反射されます。高速 PCB では、ワイヤは伝送ラインに相当する必要があります。 伝送線路の理論によれば、ソース側と負荷側のインピーダンスが同じであれば反射は起こりません。 2 つの間のインピーダンスの不一致は反射を引き起こし、負荷は電圧の一部をソース側に反射します。 負荷インピーダンスとソースインピーダンスの関係によって、反射電圧は正または負になる可能性があります . クロック信号が単調でない場合、誤ったトリガーを引き起こす可能性があります 一般的な配線ジオメトリ、不適切なワイヤ終端、コネクタを介した伝送、および電源プレーンの不連続性により、このような反射が発生する可能性があります さらに、多くの場合、1 つの出力と複数の受信機があります。 このとき、異なる配線戦略によって生成される反射は、各受信機に異なる影響を与えます。 したがって、配線戦略も無視できない要素です。 PCB 処理および PCBA 処理メーカーは、CADence に基づく高速 PCB 設計共有について説明します。