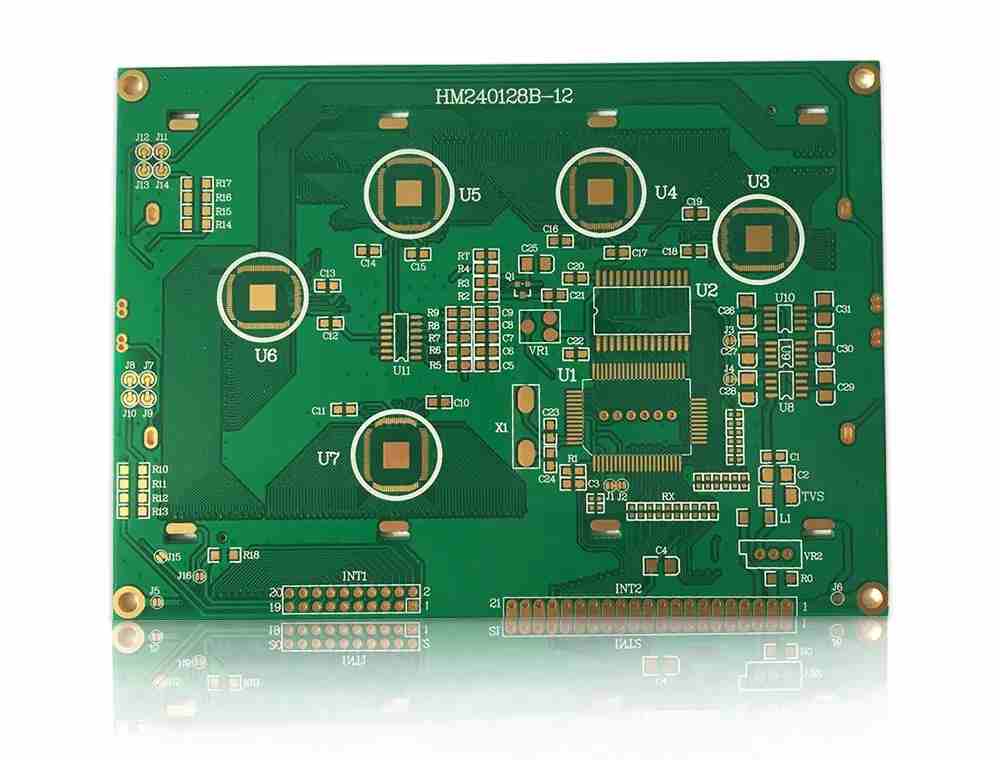

パラメトリック制約による PCB 生産の開発

現在、PCB 設計で考慮される要因は、クロック、クロストーク、インピーダンス、検出、製造プロセスなど、ますます複雑になっているため、設計者は多くのレイアウト、ルーティング、検証、メンテナンス、およびその他の作業を繰り返さなければなりません。 パラメータ制約エディタは、これらのパラメータを式に組み込むことができるため、設計者は、設計および製造プロセスで矛盾する場合があるこれらのパラメータをより適切に処理できます。

パラメトリック拘束

現在、設計ソフトウェアのサプライヤは、制約にパラメータを追加することでこの問題を解決しようとしています。 この方法の最も高度な部分は、さまざまな内部の電気的特性を完全に反映する機械的インジケーターを指定できることです。 それらが PCB 設計に追加されている限り、設計ソフトウェアはこれらの情報を使用して、自動レイアウトおよび配線ツールを制御できます。

その後の生産工程が変わっても、再設計する必要はありません。 設計者は、プロセス特性パラメータを更新するだけで、関連する制約を自動的に変更できます。 設計者は、DRC (デザイン ルール チェック) を実行して、新しいプロセスが他のデザイン ルールに違反しているかどうかを判断し、すべてのエラーを修正するために変更する必要があるデザインの側面を見つけることができます。

制約は、定数、さまざまな演算子、ベクトル、およびその他の設計制約を含む数式の形式で入力でき、設計者にパラメトリック ルール駆動システムを提供します。 制約は、テーブル ルックアップの形式で入力して、PCB または回路図デザイン ファイルに保存することもできます。 PCB 配線、銅箔領域の配置、およびレイアウト ツールは、これらの条件によって生成される制約規則に従う必要があります。 DRC は、線幅、間隔、スペース要件 (面積や高さの制限など) など、デザイン全体がこれらの制約に準拠しているかどうかを検証します。

非常に単純な例は、一般に 1.5ns の定数として設定される立ち上がり時間の制約です。 この条件によると、最大配線長の制約、つまり 5800ml/ns に立ち上がり時間 1.5ns を掛けることができます。 もう少し複雑な例は、検出角度の正接値にデバイスの高さを掛けて決定される要素間隔です。 この式は、要素間隔の最小値を計算できます。

階層管理

パラメトリック拘束の主な利点の 1 つは、階層的に処理できることです。 たとえば、グローバル ライン幅ルールは、デザイン全体のデザイン制約として使用できます。 もちろん、この原則に従えない個々のリージョンまたはノードが存在します。 この場合、上位レベルの制約をバイパスして、下位レベルの制約を階層設計に採用できます。

例として、ACCEL Technologies の制約エディター Parameter Constraint Solver を取り上げます。これには、7 つのレベルの制約があります。

1. 設計上の制約は、他の制約がないすべてのオブジェクトに適用されます。

2. 1 つのレベルのオブジェクトに対する階層的な制約。

3. タイプに含まれるすべてのノードに使用されるノード タイプ制約。

4. ノードのノード制約。

5. クラス間制約とは、2 つのタイプのノード間の制約を指します。

6. スペース内のすべてのデバイスに対するスペースの制約。

7. デバイスのデバイス制約。

ソフトウェアは、単一のデバイスから設計全体まで、ルールの順序で各設計制約に従い、ルールが設計に適用された順序をグラフィカルに表示します。 PCB design Assistant の PCB アセンブリおよび PCB 製造メーカーは、PCB 生産開発のためのパラメトリック制約の使用について説明しています。