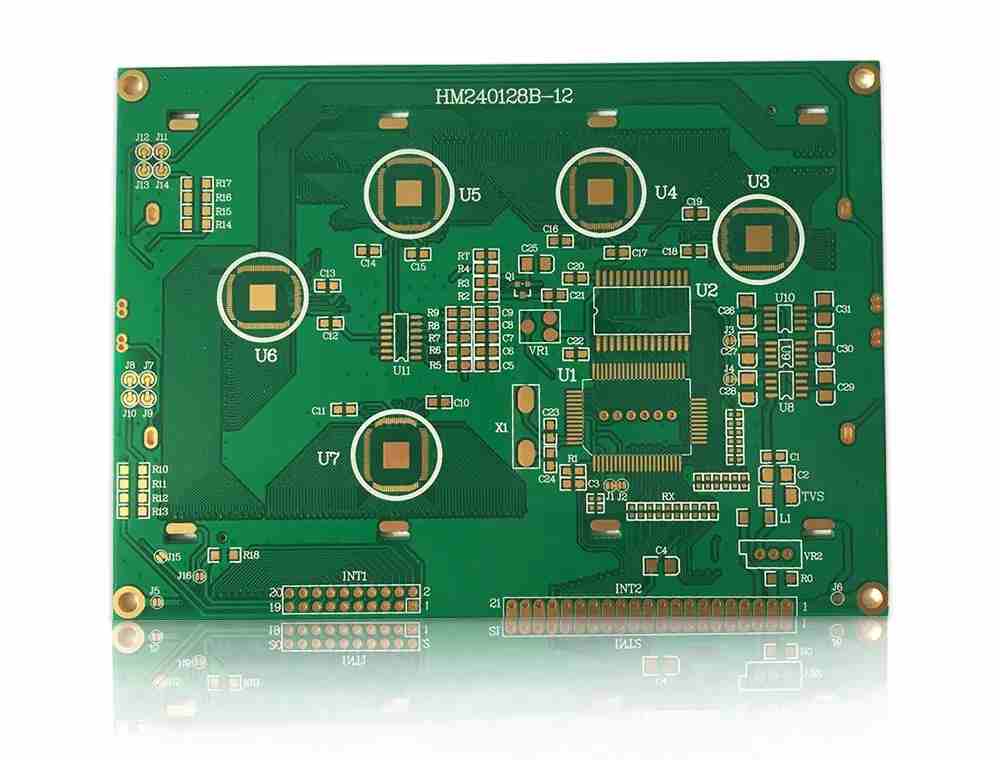

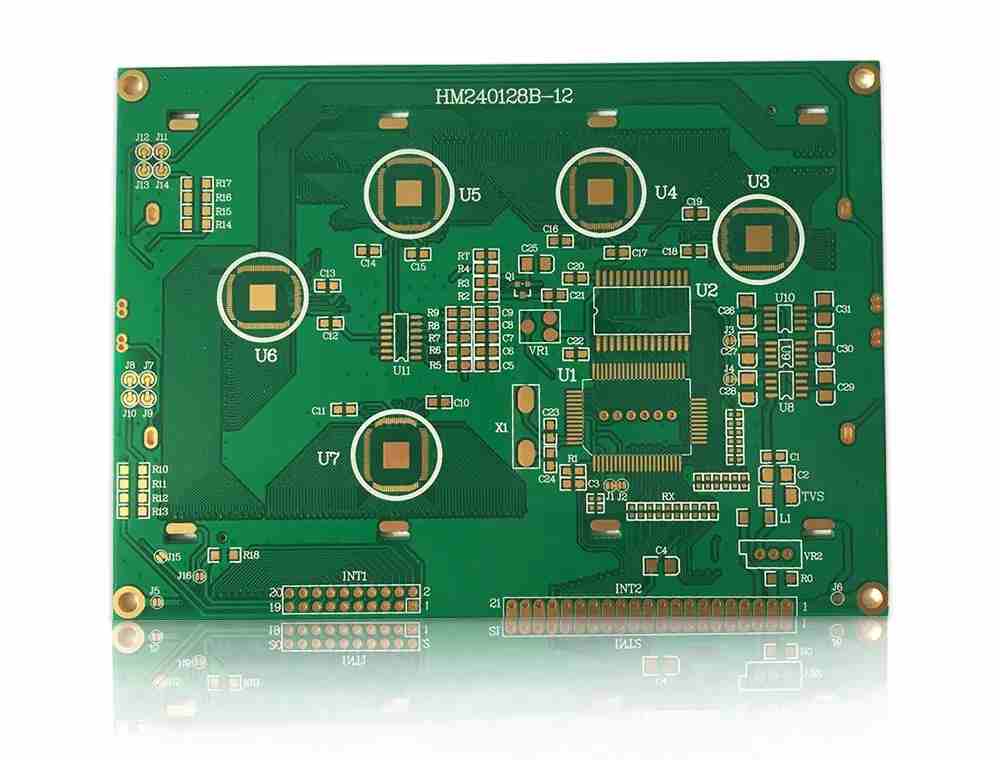

PCB アセンブリおよび PCB 処理メーカーは、EMI 放射の制御における PCB 積層の役割と設計スキルについて説明しています。

EMIの問題を解決する方法はたくさんあります。 最新の EMI 抑制方法には、EMI 抑制コーティングの使用、適切な EMI 抑制部品の選択、および EMI シミュレーション設計が含まれます。 このホワイト ペーパーでは、最も基本的な PCB レイアウトから始めて、EMI 放射の制御における PCB 積層の役割と設計スキルについて説明します。

パワーバス

適切な容量のコンデンサを IC の電源ピンの近くに適切に配置すると、IC の出力電圧のジャンプが速くなります。 しかし、問題はそれだけではありません。 コンデンサの周波数応答が限られているため、コンデンサが全周波数帯域で IC 出力をクリーンに駆動するために必要な高調波電力を生成することは不可能です。 さらに、電源バスに形成された過渡電圧は、デカップリング パスのインダクタンスの両端で電圧降下を形成し、これらの過渡電圧が主要なコモン モード EMI 干渉源になります。 これらの問題をどのように解決すべきでしょうか。

私たちの回路基板上のICに関する限り、ICの周りの電源層は、クリーンな出力のために高周波エネルギーを提供するディスクリートコンデンサによって漏れたエネルギーを収集できる優れた高周波コンデンサと見なすことができます。 また、優れた電源層のインダクタンスが小さいため、インダクタンスが合成する過渡信号が小さく、コモンモードEMIを低減します。

もちろん、電源層からICの電源端子までの接続は、デジタル信号の立ち上がりが速くなるため、できるだけ短くする必要があります。 IC の電源ピンがあるボンディングパッドに直接接続するのが良いでしょう。 これについては別途議論する必要があります。

コモン モード EMI を制御するために、電源層はデカップリングを助長し、十分に低いインダクタンスを持つ必要があります。 この電源層は、適切に設計された一対の電源層でなければなりません。 どれくらい美味しいの?と聞く人もいるかもしれません。 この質問に対する答えは、電源の層構成、層間の材料、および動作周波数 (つまり、IC の立ち上がり時間の機能) によって異なります。 一般に、電源層の間隔は 6mil で、中間層は FR4 材料で作られているため、電源層の各平方インチの等価静電容量は約 75pF です。 明らかに、層間隔が小さいほど、静電容量は大きくなります。

立ち上がり時間100~300psのデバイスは多くありませんが、現在のICの開発スピードからすると、立ち上がり時間100~300psのデバイスが高い割合を占めるようになります。 立ち上がり時間が 100 ~ 300 ps の回路の場合、3 3mil の層間隔はほとんどのアプリケーションに適していません。 当時、層間隔が 1mil 未満の積層技術を採用し、FR4 誘電体材料を高誘電率の材料に置き換える必要がありました。 現在、セラミックとセラミック プラスチックは、100 ~ 300 ps の立ち上がり時間の回路の設計要件を満たすことができます。

将来的には新しい材料と方法が使用される可能性がありますが、コモン モード EMI は、今日の一般的な 1 ~ 3 ns の立ち上がり時間の回路、3 ~ 6 ミルの層間隔、および FR4 誘電体材料の非常に低いレベルに下げることができ、通常はこれで十分です。 ハイエンドのハーモニクスを処理し、過渡信号を十分に低くします。 このホワイト ペーパーで示した PCB 積層スタック設計の例では、層の間隔が 3 ~ 6 ミルであると想定しています。

電磁シールド

信号配線の観点からは、すべての信号配線を電源層またはグランド層に近い 1 つまたは複数の層に配置することをお勧めします。 電源の場合は、電源層をグランド プレーンに隣接させ、電源層とグランド プレーンの間の距離をできるだけ小さくすることを適切な層構成にする必要があります。 これが、私たちが「レイヤリング」戦略と呼んでいるものです。

PCBスタッキング

EMI のシールドと抑制に役立つスタッキング戦略は何ですか? 次の積層構造では、電源電流が 1 つの層を流れ、単一または複数の電圧が同じ層のさまざまな部分に分散されていると想定しています。 複数の電源層の場合については後述します。

4層プレート

4 層プレートの設計にはいくつかの潜在的な問題があります。 まず、厚さが 62mil の従来の 4 層プレートの場合、信号層が外層にあり、電源層とグランド層が内層にある場合でも、電源層とグランド層の間の距離は依然として大きすぎます。 .

コスト要件が最初の場合、従来の 4 層基板に代わる次の 2 つの代替案が考えられます。 どちらの方式も EMI 抑制のパフォーマンスを向上させることができますが、ボード上のコンポーネントの密度が十分に低く、コンポーネントの周囲に十分な領域がある場合にのみ適用できます (必要な電源の銅被覆層を配置するため)。

最初のソリューションが推奨されます。 PCB の外側の層は層で、中間の 2 つの層は信号/電源層です。 信号層の電源は幅の広い配線で配線されているため、電源電流のパス インピーダンスと信号マイクロストリップ パスのインピーダンスが低くなります。 EMI 制御の観点から、これは入手可能な最高の 4 層 PCB 構造です。 2 番目の方式の外側の層は電源とグランドを使用し、中間の 2 つの層は信号を使用します。 従来の 4 層基板と比較して、この方式の改善は小さく、層間インピーダンスは従来の 4 層基板と同じくらい劣っています。

ルーティング インピーダンスを制御する必要がある場合、上記のスタッキング スキームでは、電源および接地銅アイランドの下にルーティングを配置するように十分に注意する必要があります。 さらに、DC と低周波の接続を確保するために、電源またはストラタムの銅アイランドを可能な限り相互接続する必要があります。

6層プレート

4 層基板の部品密度が比較的大きい場合は、6 層基板を使用することをお勧めします。 ただし、6 層基板設計の一部のスタック方式では、電磁界を十分にシールドできず、電源バスの過渡信号の低減にはほとんど効果がありません。 以下に 2 つの例を示します。

最初の例では、電源とグランドはそれぞれ 2 層目と 5 層目に配置されます。 電源の銅クラッド インピーダンスが高いため、コモン モード EMI 放射を制御することは非常に好ましくありません。 ただし、信号インピーダンス制御の観点からは、この方法は非常に正しいです。

2 番目の例では、電源とグランドはそれぞれ 3 層目と 4 層目に配置されます。 この設計は、電源の銅被覆インピーダンスの問題を解決します。 第 1 層と第 6 層の電磁シールド性能が低いため、ディファレンシャル モード EMI が増加します。 2 つの外側層の信号線の数が最小で、配線長が非常に短い (信号の最高高調波波長の 1/20 より短い) 場合、この設計は差動モード EMI 問題を解決できます。 外層のコンポーネントおよび配線のない領域が銅で満たされ、銅で覆われた領域が接地されている場合 (1/20 波長ごとに 1 つの間隔)、ディファレンシャル モード EMI は特に十分に抑制されます。 前述のように、銅敷設エリアは複数のポイントで内部グランド プレーンに接続する必要があります。

一般的には、1層目と6層目は地層として配置され、3層目と4層目は電源と接地されています。 電源層とグランド層の間に2層のダブルマイクロストリップ信号ラインがあるため、EMI抑制能力に優れています。 この設計の欠点は、ルーティング層が 2 つの層しかないことです。 前述のように、外層配線が短く、配線のない部分に銅を敷けば、従来の6層基板でも同様の積層が実現できます。

もう 1 つの 6 層基板レイアウトは、信号、グランド、信号、電源、グランド、および信号であり、高度なシグナル インテグリティ設計に必要な環境を実現できます。 信号層はグランド プレーンに隣接し、電源層はグランド プレーンと対になっています。 明らかに欠点は、層が不均一に積み上げられることです。

これは通常、処理と製造に問題をもたらします。 この問題の解決策は、3 番目の層のすべての空白領域を銅で埋めることです。 第 3 層の銅メッキ密度が、銅充填後の電源層またはグランド プレーンに近い場合、この基板はバランスの取れた構造の回路基板と大まかに見なすことができます。 銅充填領域は、電源またはグランドに接続する必要があります。 接続するビア間の距離は依然として 1/20 波長です。 どこでも接続できるわけではありませんが、理想的には接続する必要があります。

10枚合板

多層基板間の絶縁分離層は非常に薄いため、10 層または 12 層の回路基板の層間インピーダンスは非常に低くなります。 重ね付けや積み重ねに問題がなければ、優れたシグナルインテグリティが期待できます。 62milの厚さに合わせて12層の基板を加工して製造するのはより難しく、12層の基板を加工できるメーカーはほとんどありません。

信号層とループ層の間には常に絶縁層があるため、10 層基板設計で信号線を取るために中間の 6 層を割り当てるのは最善の方法ではありません。 また、信号層をループ層に隣接させること、つまりボードレイアウトを信号、グランド、信号、信号、電源、グランド、信号、グランド、信号にすることが重要です。

この設計は、信号電流とそのループ電流に適切な経路を提供します。 適切な配線戦略は、X 方向に沿って最初の層を配線し、Y 方向に沿って 3 番目の層を配線し、X 方向に沿って 4 番目の層を配線することです。 ルーティングを視覚的に表示します。 1層目と3層目は重ね合わせのペア、4層目と7層目は重ね合わせのペア、8層目と10層目は最後の重ね合わせのペアです。 引き回し方向を変更する必要がある場合は、1 層目の信号線を「ビア」で 3 層目に変更する必要があります。 実際、必ずしもそうとは限りませんが、設計思想として可能な限り従うべきです。

同様に、信号の引き回し方向が変わる場合は、レイヤ 8 とレイヤ 10 から、またはレイヤ 4 からレイヤ 7 にビアで接続する必要があります。 この配線により、フォワード パスと信号のループとの間のカップリングが最も密になります。 たとえば、信号がレイヤ 1 にルーティングされ、回路がレイヤ 2 にルーティングされ、レイヤ 2 のみにルーティングされる場合、レイヤ 1 の信号が「ビア」を介してレイヤ 3 に転送されたとしても、回路は依然としてレイヤ上にあります。 2、したがって、低インダクタンス、大容量、および良好な電磁シールド性能の特性を維持します。

実際のルーティングがこのようでない場合はどうなりますか? 例えば、1層目の信号線はビアを経由して10層目に至る。 このとき、ループ信号は第 9 層からグランド プレーンを見つける必要があり、ループ電流は最も近いグランド ビア (抵抗やコンデンサのグランド ピンなど) を見つける必要があります。 このようなビアが近くにあればラッキーです。 そのようなビアが近くにない場合、インダクタンスが大きくなり、静電容量が減少し、EMI は確実に増加します。

信号線が現在のペアの配線層からビアを介して他の配線層に出なければならない場合、ループ信号が適切な接地層にスムーズに戻るように、接地ビアをビアの近くに配置する必要があります。 レイヤ 4 とレイヤ 7 のレイヤリングの組み合わせの場合、信号回路は電源レイヤまたはグランド レイヤ (つまり、レイヤ 5 またはレイヤ 6) から戻ります。 伝達しやすい。

複数の電源層の設計

同じ電圧源の 2 つの電源層が大電流を出力する必要がある場合、回路基板は電源層と接地層の 2 つのグループに分けられます。 この場合、絶縁層は、電源層の各ペアとグランド プレーンの間に配置されます。 このようにして、電流を均等に分割する同じインピーダンスを持つ 2 組の電源バスバーを得ることができます。 電源層の積み重ねによってインピーダンスが等しくない場合、シャントが不均一になり、過渡電圧がはるかに大きくなり、EMI が急激に増加します。

回路基板上に値の異なる複数の電源電圧が存在する場合、それに応じて複数の電源層が必要になります。 異なる電源用に電源層とグランド層のペアを作成することを忘れないでください。 上記の 2 つのケースでは、回路基板上の一対の電源層とグランド プレーンの位置を決定する際に、バランスのとれた構造に対するメーカーの要件を思い出してください。

まとめ

エンジニアによって設計された回路基板のほとんどは、厚さ 62mil の従来のプリント回路基板であり、ブラインド ホールや埋め込み穴がないため、このホワイト ペーパーでの回路基板のレイヤリングとスタッキングに関する説明はこれに限定されます。 厚さの差が大きすぎる回路基板の場合、このホワイト ペーパーで推奨されている積層方式は理想的ではない場合があります。 さらに、このホワイト ペーパーの剥離方法は、処理プロセスが異なるため、止まり穴または埋め込み穴のある PCB には適用できません。

回路基板の設計において、回路基板の厚さ、ビア プロセス、および層の数は、問題を解決するための鍵ではありません。 電源バスのバイパスとデカップリングを確実にし、電源層またはグランド層の過渡電圧を最小限に抑え、信号と電源の電磁界をシールドするには、優れた積層スタックが重要です。 理想的には、信号配線層とそのループ グランド層の間に絶縁層があり、整合層の間隔 (またはペア以上) はできるだけ小さくする必要があります。 これらの基本的な概念と原則に従って、設計要件を常に満たすことができる回路基板を設計できます。 現在、ICの立ち上がり時間は非常に短く、さらに短くなります。 このホワイト ペーパーで説明する技術は、EMI シールドの問題を解決するために不可欠です。 PCB アセンブリおよび PCB 処理メーカーは、EMI 放射の制御における PCB 積層の役割と設計スキルについて説明しています。