PCB を超えて: 高速問題のシステム レベルの考察

回路基板アセンブリ メーカーは、高速で高密度の PCB 設計が直面する新しい課題について説明しています。高速の問題に対するシステム レベルの考察

システムが数百メガバイトから数十ギガバイトに発展すると、チップ設計、パッケージ設計、システム設計は切り離して考えることができなくなります。 ハイエンド製品の場合、チップを設計する際にパッケージ設計とシステム設計を考慮する必要があります。

ソフトウェア自体の問題を取り除いた後、いかにプロセスを合理化し、エンジニアのプロセスでのミスを減らし、エンジニアがより多くのエネルギーを設計に投入できるようにし、製品をできるだけ早く市場に投入できるようにするかという内容にもなりました。 EDAメーカーが検討中。

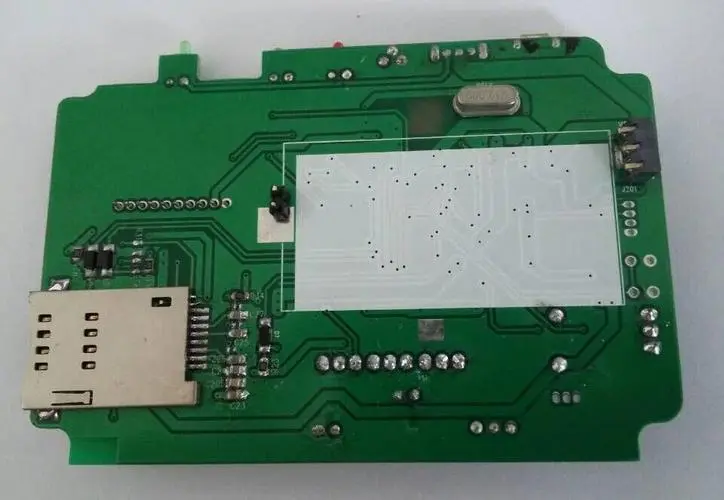

通常、システム上の接続ラインは、シリコンの I/O から始まり、パッケージのバンプとサブセットを通り、カプセル化されたピンに到達し、PCB を通り、他のカプセル化されたピン、サブセット、バンプ、および I に到達します。 /チップのO。 チップ、パッケージ、および回路基板は、3 つの異なる領域です。 以前のエンジニアは、設計時にそれらを包括的に考慮していませんでしたし、他のエンジニアが何を考えているかも知りませんでした。 しかし、設計頻度の増加、チップ面積の縮小、および設計サイクルの短縮に伴い、メーカーはチップを設計する際にパッケージ設計と PCB 設計を考慮して、3 つを効果的に組み合わせる必要があります。 Chen Lanbing 氏は次のように述べています。 PCB で解決しますが、パッケージで簡単に解決できます。」

システム レベルのプロセス設計を積極的に支持するケイデンスの Allegro プラットフォームは、ボード レベルの設計とパッケージ レベルの設計をカバーし、ケイデンスの他のいくつかのチップ設計プラットフォームと接続して、完全な設計チェーンを形成し、効果的なデータ交換と通信を実現できます。 また、ケイデンスの VSIC (Virtual System InterConnect) 設計手法は、エンジニアが設計の初期段階でシステム全体に起因するタイミングやシグナル インテグリティの問題を考慮することを可能にする新しいシリコン パッケージ ボード共同設計手法であり、設計における大きなボトルネックを解決します。 ギガヘルツ信号の設計。 回路基板アセンブリおよび回路基板処理メーカーは、高速で高密度の PCB 設計が直面する新しい課題について説明しています。システム レベルでの高速な考慮事項