従来のSDRAMインターフェース回路と比較して、回路の電気的パラメータに対する登録SDARM回路の設計制約は比較的緩く、主制御チップの駆動能力は基本的に設計で考慮されていません。 ただし、Registered SDRAM は高速インターフェイス回路でもあるため、設計された回路の信頼性と安定性を確保するために、その回路設計も一定のルールに従う必要があります。

(1) 基本設計ルール

① 各チップのクロック入力に位相調整コンデンサを設計しています。 静電容量値は10pFに設定でき、測定データに応じて調整できます。

② 各 SDRAM チップのデータピンには、整合抵抗が直列に設計されています。 マッチング抵抗値は10Ωまで設定可能です。

③ 各ラッチチップのラッチクロックは、クロック拡張回路の出力クロックが異なります。

④ 各 SDRAM チップの入力クロックは、クロック拡張回路の出力クロックが異なります。

⑤ クロック拡張チップのクロック出力端子には直列整合抵抗を設計しています。 マッチング抵抗値は10Ωまで設定可能です。

⑥ ラッチチップの出力はマッチング抵抗を直列に接続した設計になっています。 マッチング抵抗値は10Ωまで設定可能です。

(2) ボードルーティング規則

① SDRAM データケーブル: MPC824l から同じ SDRAM チップへのデータ信号ルーティングは、等しい長さで制御する必要があり、長さの誤差は ± 5% 以内に制御する必要があります。

②SDRAMアドレス/コントロールライン:ラッチチップからSDRAMへ

チップのアドレス/制御信号ルーティングは、等長で制御する必要があり、長さの誤差は ± 5% 以内に制御する必要があります。

③ クロック拡張回路はラッチチップに 2 ウェイラッチクロックを出力します。 その配線は等長に管理する必要があり、長さの誤差は±27mm以内に抑えられています。

④ クロック拡張回路は 4 ウェイクロックを SDRAM チップに出力し、その引き回しは等長で管理する必要があり、長さ誤差は ±1 以内 27mm 以内。

⑤ ラッチチップから SDRAM チップまでのアドレス/制御信号は、クロック拡張回路から対応する SDRAM チップまでのクロックラインと基本的に同じ長さであり、長さ誤差は±5%以内に抑えられています。

⑥クロック拡張回路のフィードバッククロック配線長は、基本的にクロック拡張回路からSDRAMチップまでの平均クロック配線長と等しく、長さ誤差は±10%以内に抑えられています。

⑦ MPC824l と SDRAM チップ間のデータ線、アドレス線、制御線、クロック線の配線長は基本的に等しく、長さ誤差は ± 10% 以内に抑えられています。

(3) レイアウトルール

① 位相調整用コンデンサはすべて受電側に配置。

② クロックシリーズの整合抵抗は全て送信端近くに配置。

③ SDRAM チップのデータ端子の直列整合抵抗が SDRAM チップに近い。

④ラッチチップの出力端の直列整合抵抗を出力端の近くに配置する。

(4) その他のデザインルール

① 配線ごとにインピーダンス管理を行い、片端配線のインピーダンスは 50 Ωとする。

② チップの電源端子にはデカップリングコンデンサを実装する必要があり、その容量値は 1 μF です。 原則として、各電源端子にはデカップリングコンデンサを設計し、電源端子のできるだけ近くに配置する必要があります。

③ 完全な階層と電源層は、少なくとも完全な階層を確保する必要があります。

④ クロック信号は、EMI を低減するために、可能な限り内層に到達する必要があります。

(5) 設計回路のデバッグ

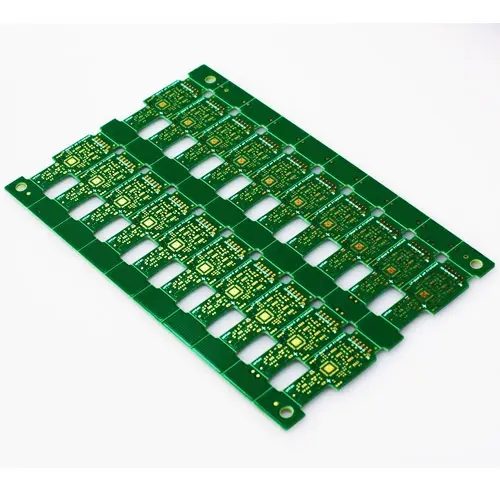

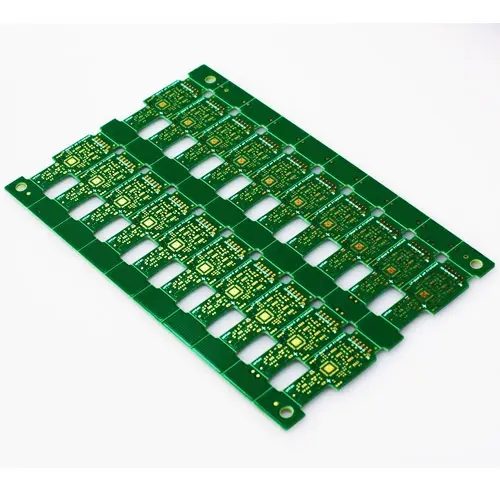

上記のルールに従って設計されたハードウェア pcb 回路は、位相調整容量をわずかに調整するだけで、100 MHz の SDRAM クロックで安定して動作します。 位相調整容量の範囲は、一般的に 5 ~ 15pF です。 タイミング パラメータのマージンが十分にある場合は、位相調整コンデンサを溶接せずに残すこともできます。 回路基板メーカーは、SDRAM の原理設計と回路基板設計のレイアウト規則について説明します。