Key Points of PCB Design with High Speed Programmable Gate Array

As field programmable gate array (FPGA) has developed into a true on-chip programmable system, the task PCB designed has become more complex with these chips The current circuit density of millions of gates, the transceiver data rate exceeding 6 Gbps and other considerations will affect the mechanICal and power board level design work of system developers In this system, the function of programmable gate array is fully realized. The printed circuit board needs to be carefully designed When using high-speed programmable gate array design, it is important to consider several design issues before and during the development of the board These measures include: reducing system noise by filtering and evenly distributing sufficient power on all devices on the PCB; Terminate the signal line appropriately to minimize reflection; Minimize crosstalk between traces on the board; Reduce the impact of ground rebound and Vcc reduction (also known as Vcc depression); Correctly match the impedance of high-speed signal line. Anyone who designs integrated circuit packages for high-performance programmable gate arrays must pay special attention to the balance between signal integrity and versatility of all users and applications For example, Stratix II GX equipment of Altera Corporation operates in a 508 pin package to 1.2 volts and features 734 standard I/Os and 71 low-voltage differential signal (LVDS) channels. It also has 20 high-speed transceivers that support data rates of up to 6.5 percent 375Gbps。 This enables the architecture to support many high-speed network and communication bus standards, including PCI Express bus and SerialLite II series.

Printed circuit board

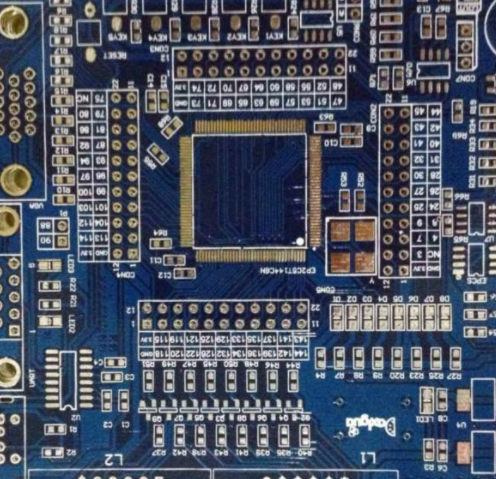

In PCB design, users can reduce crosstalk by optimizing pins The signal pin should be as close to the grounding pin as possible to reduce the loop length within the package, especially for critical high-speed input/output. In high-speed systems, the main source of crosstalk is inductive coupling between signal paths within the package When the output is converted, the signal must find its return path/ground plane through the power supply Changes in the current in the circuit will create a magnetic field, causing pins near other input/output circuits This situation is aggravated when the output is switched SIMultaneously Because the SMAller the loop, the smaller the inductance. In summary, installing a power supply or grounding pin package near each high-speed signal pin can minimize crosstalk to nearby input/output pins In order to reduce the cost of the circuit board, improve the system signal integrity of all signal paths, and carefully design and build the board, the number of layers (stacks) and layout are required. Sending hundreds of signals from the programmable gate array to or around the circuit board is a difficult task, which requires the use of electronic data analysis tools to optimize the pin and chip layout Sometimes, a slightly larger programmable gate array package can reduce the cost of the circuit board because it reduces the number of layers on the circuit board and other circuit board processing constraints

The high-speed signal path opens the printed circuit board, which is represented by the circuit board track that is very sensitive to interruption, such as the via between the circuit board layer and the circuit board connector These and other interruptions reduce the edge rate of the signal, causing reflections Therefore, designers should avoid via and via stubs If vias are unavoidable, keep the vias wires as short as possible When routing differential signals, use vias with the same structure for each path of the differential pair; This makes the signal interruption caused by the through-hole common mode If possible, use blind vias as opposed to conventional vias Or use reverse drilling, because there is less interruption due to the loss of through hole root

To improve the signal integrity of the clock signal, the following guidelines should be followed: Before sending the clock signal to the Circuit board assembly, keep it on the single board layer as much as possible; Always use a plane as the reference plane Fast edge signals are sent along the inner layer near the ground plane to control impedance and reduce electromagnetic interference Terminate the clock signal correctly to minimize reflections Use point-to-point clock tracking

Some FPGAs, such as Stratix II GX series, support multiple input/output standards These on-chip resistors can be set as 25 ohm or 50 ohm single ended resistors, and support LVTTL, LVCMOS, and stainless steel - 18 or SSTL-2 single ended input/output standards; In addition, 100 ohm left ventricle and super transmit input support on-chip differential matching resistor The differential transceiver I/O system has a programmable on-chip resistor of 100, 120 or 150 ohms, automatic calibration and reflection Using internal resistors instead of external devices has several advantages for the system On chip terminals improve signal integrity by eliminating lead wire effects and realizing reflection on transmission lines On chip termination also minimizes the number of external components required, allowing designers to use fewer resistors, fewer board traces, and less board space With this pipeline, the layout can be simplified, the design cycle can be shortened, and the system cost can be reduced Because there are fewer components on the circuit board, the reliability of the circuit board has also been enhanced In Board Design, there are several criteria for routing microstrip and stripline to minimize crosstalk For the double strip line layout, the wiring is carried out on two layers of inner plates, with a voltage reference plane on both sides At this time, all wires of adjacent layers use orthogonal wiring technology to maximize the use of the medium between the two signal layers Data thickness, and normalize the distance between each signal layer and its adjacent reference plane, while maintaining the required impedance

Microstrip or stripline wiring guide, with the line spacing at least 3 times the thickness of the dielectric layer between the wiring layers of the circuit board; Use the analogy tool to pre analogy its behavior For key high-speed networks, differential topology is used instead of single ended topology to minimize the impact of common mode noise Within the design limits, try to match the positive and negative pins of the differential signal path Reduce the coupling effect of single ended signals, leave appropriate spacing (more than three times the trace width), or wire on different board layers (wiring of adjacent layers is orthogonal to each other). Moreover, the use of analogy tools is a good way to meet the spacing requirements Minimize the parallel length between signal terminals At the same time, during the discharge and charging of the signal path of the clock and I/O type, the data rate increases with the corresponding reduction of the output conversion times, and the transient current also increases These currents may cause board level ground rebound, transient rise/ground voltage drop/Vcc. The large transient current from the non ideal power supply will cause the instantaneous drop of Vcc (Vcc drop or drop). Here are some good circuit board design rules to help reduce the impact of simultaneous transition noise Include unused I/O pins as outputs and drive them to a lower position to reduce ground bounce Minimize the number of simultaneous conversion output pins and evenly distribute them in the entire FPGA I/O type part When high edge rate is not required, low conversion rate is used at the output of the programmable gate array The voltage cc is placed between the grounding layers of the Multilayer board to eliminate the influence of high-speed traces on each layer All circuit board layers are dedicated to voltage cc and grounding to make these planes have resistance and inductance, provide a low inductance source with low capacitance and noise, and return logical signals on the signal layers adjacent to these planes

Pre emphasis

The high speed transceiver capability of FPGA makes it a highly efficient programmable system on chip component, but they also bring unique challenges to circuit board designers The key problem, especially related to the layout, is frequency related transmission loss, which is mainly caused by skin effect and dielectric loss When the high-frequency signal is transmitted on the conductor surface (such as PCB), the skin effect is caused by the self induction of the conductor This effect reduces the effective conducting area of the wire and attenuates the high-frequency component of the signal Dielectric loss is caused by the capacitance effect of interlayer dielectric materials The skin effect is proportional to the square root of the frequency, and the dielectric loss is proportional to the frequency; Therefore, dielectric loss is the main loss mechanism of high-frequency signal attenuation The higher the data rate, the more serious the skin effect and dielectric loss For a 1Gbps system, the signal level reduction on the link is acceptable, but not for a 6Gbps system However, today's transceivers have transmitter pre emphasis and receiver equalization functions to compensate for high frequency channel distortion They also enhance signal integrity and ease tracking length constraints These signal conditioning technologies extend the life of standard page 4 data and support higher data rates Due to the signal attenuation in the data on page 4, when working at 6.0 ℃, the allowable track length is limited to several inches. 375Gbps. Preweight and equalization can be extended to more than 40 inches The programmable design pre emphasis and balance are integrated into some high-performance programmable gate arrays, such as Stratix II GX equipment, allowing the use of page 4 data, and relaxing layout constraints, such as track length, to reduce the cost of the board of directors The pre emphasis function can effectively enhance the high frequency components of the signal The 4-tap pre emphasis circuit in Stratix II GX reduces signal component scattering (spatial spread from one bit to another). The pre emphasis circuit provides 500% pre emphasis. According to the data rate, each tap can be optimized to 16 levels, track length and connection characteristics In addition to the input gain stage, the device allows the circuit board designer to have an equalization level of 17 dB, using any of the 16 equalizer stages to overcome the circuit board loss Equalization and pre emphasis can be used to coordinate the environment or individually optimize specific links When the system is running, the designer can change the pre emphasis and equalization levels in the Stratix II GX FPGA, or during the card configuration after inserting the card into the backplane or other main chassis This gives the system designer the flexibility to automatically set the pre emphasis and equalization levels to predetermined values Alternatively, these values can be dynamically determined based on the slot in which the board is inserted into the chassis or backplane

EMI problems and debugging

The EMI caused by the printed circuit board is proportional to the change of current or voltage with time, and the series inductance of the circuit Efficient circuit board design may minimize electromagnetic interference, but may not eliminate it completely The elimination of "intruder" or "thermal" signals and the transmission of signals to ground level with appropriate reference will also help to reduce electromagnetic interference, It is also a method to reduce electromagnetic interference by using surface mount components that are common in the MARKet today Debugging and testing complex high-speed data is becoming more and more difficult. Because of some traditional single board debugging methods, such as test probes and "nail bed" testers, printed circuit boards may not be suitable for these designs. This new high-speed design can make use of the j tag testing tool, as well as the possible in system programming and built-in self-test functions of programmable gate arrays The designer should use the same guidelines to set the JTAG test clock input (TCK) signal to the system clock. In addition, it is important to keep the tracking length of the j tag scanning chain between the test data output of one device and the test data login of another device to a minimum Successful design using embedded high-speed programmable gate array requires a lot of high-speed board design practice, as well as a solid understanding of programmable gate array functions (such as pins), board and stack, circuit board layout, and termination mode It is also important to use the pre emphasis and equalization of the included transceiver correctly The above points are combined to achieve reliable design with stable manufacturability Careful consideration of all these factors, combined with appropriate analogy and analysis, can reduce the possibility of accidents and will help reduce the pressure on the board of directors to develop projects