組み込みシステムで PCB 信号の完全性を向上させる方法

回路基板製造、回路基板設計、および PCBA 処理メーカーが、組み込みシステム PCB 信号の完全性を向上させる方法を説明します

電子技術の絶え間ない進歩に伴い、ますます多くの分野が組み込みシステムに適用されます。 これらの数多くのアプリケーションの中で、人々はもはや機能や性能ではなく、信頼性や互換性を考慮しています。 そして、配線技術により組み込みシステムPCBのシグナルインテグリティをいかに向上させるかが「重要なテーマ」となっています。

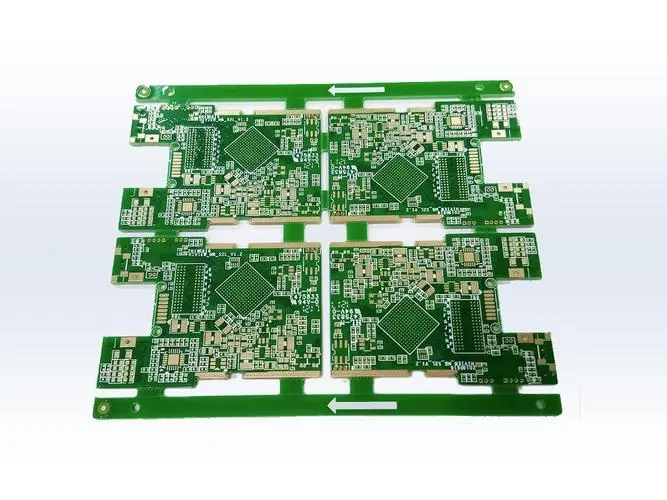

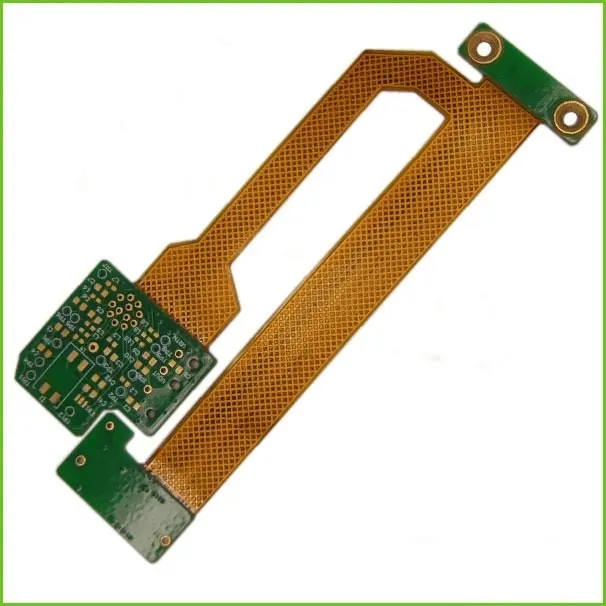

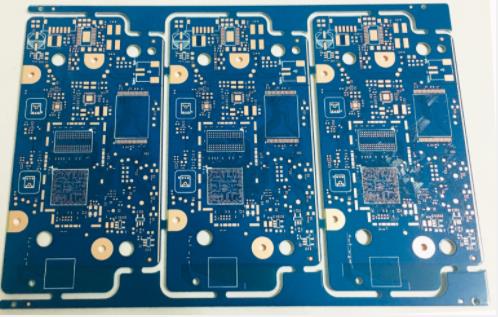

周知のように、PCB (プリント回路基板) は電子製品の回路コンポーネントとデバイスの基本的なサポートであり、その設計品質は多くの場合、組み込みシステムの信頼性と互換性に直接影響します。 これまで、一部の低速回路基板では、クロック周波数は一般的にわずか 10 MHz 程度でした。 回路基板またはパッケージ設計の主な課題は、2 層基板上のすべての信号線を配線する方法と、組み立て中にパッケージを損傷しない方法です。

相互接続の電気的特性は、システムのパフォーマンスに影響を与えないため重要ではありません。 この意味で、低速信号回路基板内の相互接続は滑らかで透過的です。 しかし、組み込みシステムの発展に伴い、使用される回路は基本的に高周波回路です。 クロック周波数が高くなると、信号の立ち上がりエッジも短くなります。 通過する信号に対するプリント回路の容量性リアクタンスと誘導性リアクタンスは、プリント回路自体の抵抗よりもはるかに大きくなり、信号の完全性に深刻な影響を与えます。 組み込みシステムでは、クロック周波数が 100 MHz を超えるか、立ち上がりエッジが 1 ns 未満になると、シグナル インテグリティの影響が重要になります。

PCB では、信号線が信号伝送のメイン キャリアです。 信号線のルーティングは、信号伝送の優位性を直接決定するため、組み込みシステム全体のパフォーマンスに直接影響します。 無理な配線は、さまざまなシグナル インテグリティの問題を引き起こし、回路にタイミング、ノイズ、および電磁干渉 (EMI) を発生させ、組み込みのパフォーマンスに深刻な影響を与えます。 本稿では、高速デジタル回路における信号線の実際の電気的特性から出発して、電気的特性モデルを確立し、信号の完全性に影響を与える主な理由と問題を解決する方法、および解決すべき問題を見つけます。 注意を払い、配線で従うべき方法とスキルが示されています。

信号の完全性

シグナル インテグリティとは、信号ライン上の信号の品質、つまり、信号が回路内の正しいタイミングと電圧レベルで応答する能力を指します。 信号の完全性が良好な信号とは、必要なときに必要な電圧レベル値を持つことを意味します。 シグナル インテグリティの低下は、単一の要因ではなく、ボード レベルの設計における複数の要因によって引き起こされます。 シグナル インテグリティの問題は、主に遅延、反射、クロストーク、オーバーシュート、発振、アース ボムなど、さまざまな側面に反映されます。

遅延: 遅延とは、PCB ボードの伝送ライン上で信号が制限された速度で伝送され、信号が送信側から受信側に送信され、その間に伝送遅延があることを指します。 信号遅延は組み込みタイミングに影響します。 伝送遅延は、主にワイヤの長さとワイヤ周囲の媒体の誘電率に依存します。 高速デジタルシステムにおいて、信号伝送ラインの長さは、クロックパルスの位相差に影響を与える最も直接的な要因です。 クロックパルスの位相差とは、同時に生成された2つのクロック信号が同期して受信機に到達しないことを指します。 クロックパルスの位相差は、信号の到着の予測可能性を低下させます。 クロック パルスの位相差が大きすぎると、受信側でエラー信号が生成されます。

反射: 反射は、信号線上の信号のエコーです。 信号の遅延時間が信号のジャンプ時間よりもはるかに大きい場合、信号ラインは伝送ラインと見なす必要があります。 伝送線路の特性インピーダンスが負荷インピーダンスと一致しない場合、信号電力 (電圧または電流) の一部が伝送されて負荷に到達しますが、その一部は反射されます。 負荷インピーダンスが元のインピーダンスよりも小さい場合、反射は負になります。 それどころか、反省はポジティブです。 配線形状の変更、不適切な配線終端、コネクタを介した伝送、および電源プレーンの不連続により、このような反射が発生する可能性があります。

クロストーク: クロストークとは、2 つの信号線間の結合、信号線間の相互インダクタンスおよび相互容量によって生じる信号線上のノイズを指します。 容量結合は結合電流につながり、誘導結合は結合電圧につながります。 クロストークノイズは、信号線間、信号系と配電系、ビア間の電磁結合に起因します。 シリアル巻線は、誤ったクロック、間欠的なデータ エラーなどを引き起こし、隣接する信号の伝送品質に影響を与える可能性があります。 実際には、クロストークを完全になくすことはできませんが、システムが耐えられる範囲で制御できます。 PCB 層パラメータ、信号線間隔、ドライバとレシーバの電気的特性、およびベースライン終端モードは、クロストークに一定の影響を与えます。

オーバーシュートとアンダーシュート: オーバーシュートとは、設定電圧を超える最初のピーク値または谷値を指します。 立ち上がりエッジでは、最高電圧を指します。 立ち下がりエッジの場合は、最低電圧を指します。 ダウンラッシュとは、設定電圧を超える次の谷値またはピーク値を指します。 オーバーシュートが大きすぎると、保護ダイオードが機能し、早期の故障につながる可能性があります。 過剰なアンダーシュートは、誤ったクロックまたはデータ エラー (誤動作) を引き起こす可能性があります。

発振とサラウンド発振:オーバーシュートとアンダーシュートを繰り返す発振現象。 信号発振は線路上を遷移するインダクタンスとキャパシタンスによって引き起こされます。これはアンダー ダンピング状態に属し、周囲の振動はオーバー ダンピング状態に属します。 反射と同様に、振動やサラウンド振動も多くの要因によって引き起こされます。 適切な終端処理を行うことで発振を抑えることはできますが、完全になくすことはできません。

グランド レベル バウンス ノイズとリターン カレント ノイズ: 回路に大きな電流サージがあると、グランド レベル バウンス ノイズが発生します。 たとえば、多数のチップ出力が同時にオンになると、チップとボードの電源プレーンに大きな過渡電流が流れ、チップ パッケージと電源プレーンのインダクタンスと抵抗によって、 電源ノイズは、実際のグランドプレーンで電圧変動と変化を引き起こします。このノイズは、他のコンポーネントの動作に影響を与えます。 負荷容量の増加、負荷抵抗の減少、グランド インダクタンスの増加、およびスイッチング デバイスの数の増加は、グランド スプリングの増加につながります。

伝送路の電気特性解析

多層 PCB では、ほとんどの伝送線路が 1 つの層に配置されるだけでなく、複数の層に互い違いに配置され、層はビアを介して接続されます。 したがって、多層PCBでは、典型的な伝送チャネルは主に伝送ライン、配線コーナー、ビアの3つの部分で構成されます。 低周波数の場合、プリント ワイヤと配線ビアは、異なるデバイス ピンを接続する共通の電気接続と見なすことができ、信号品質に大きな影響を与えることはありません。 ただし、高周波の場合、プリント ワイヤ、コーナー、およびビアは、それらの接続性を考慮するだけでなく、高周波での電気的特性と寄生パラメータも考慮することができます。

高速 PCB の伝送線路の電気的特性の解析

高速 PCB の設計では、長さの異なる多数の信号接続ラインを使用することは避けられません。 信号自体の変化時間と比較すると、接続線を通過する信号の遅延時間は無視できません。 信号は、電磁波の速度で接続線上を伝送されます。 このとき、接続線は抵抗、静電容量、インダクタンスの複雑なネットワークであり、分布定数系モデル、つまり伝送線路モデルで記述する必要があります。

伝送線路は、一方の端から他方の端まで信号を伝送するために使用されます。 これは、一定の長さの 2 本のワイヤで構成され、一方はシグナル パスと呼ばれ、もう一方はリターン パスと呼ばれます。 低周波回路では、伝送線路の特性は純抵抗の電気特性として表されます。 高速 PCB では、伝送信号の周波数が高くなると、導体間の容量性インピーダンスが減少し、導体上の誘導性インピーダンスが増加します。 信号線はもはや純粋な抵抗を示すだけではありません。つまり、信号は導体上を伝送するだけでなく、導体間の媒体も伝送します。 信号周波数がさらに増加すると、j ω L>>R のとき、1/(j ω C) < 一様導体の場合、伝送線路の抵抗 R、寄生インダクタンス L、および寄生容量 C の平均分布 (つまり、L1=L2= ...=Ln; C1=C2=...=Cn+1) 外部環境の変化を考慮せずに PCB メーカー、PCB 設計者、および PCBA メーカーは、組み込みシステムにおける PCB 信号の完全性を向上させる方法を説明します。