PCBメーカー、PCB設計者、PCBAメーカーが高速FPGAをベースとしたPCB設計技術を解説

高速 PCB 設計が、回路図ノードを接続するのと同じくらい簡単で、コンピューターのディスプレイに表示されるのと同じくらい美しいものになるとしたら、それは素晴らしいことです。 ただし、設計者が PCB 設計に慣れていないか、非常に幸運でない限り、通常、実際の PCB 設計は彼らが従事している回路設計ほど簡単ではありません。PCB 設計者は、設計が正常に機能し、性能が確認されるまでに、多くの新しい課題に直面します。 これは、まさに高速 PCB 設計の現在の状況です。設計ルールと設計ガイドラインは常に開発されています。 運が良ければ、彼らは成功する解決策を形成します。

ほとんどの PCB は、PCB デバイスの動作原理と相互影響に精通した回路図設計者と、回路基板の入出力を構成するさまざまなデータ伝送規格と、ほとんど知らないプロのレイアウト設計者との間の相互協力の結果です。 または、小さな回路図のワイヤをプリント回路の銅線に変換した後に何が起こるかわからない場合さえあります。 通常、最終的な回路基板の成否に責任を持つのは回路図設計者です。 ただし、回路図設計者が優れたレイアウト テクノロジについて知れば知るほど、大きな問題を回避する機会が増えます。

設計に高密度 FPGA が含まれている場合、慎重に設計された回路図の前に多くの課題が発生する可能性があります。 何百もの入力ポートと出力ポートの数、500MHz を超える動作周波数 (一部の設計ではより高い場合があります)、および 0.5 mm ほどのはんだボール間のスペースなど、これらすべてが設計ユニット間の過度の相互作用を引き起こします。

同時スイッチング ノイズ

最初の課題はおそらく、いわゆる同時スイッチング ノイズ (SSN) または同時スイッチング出力 (SSO) です。 大量の高周波データ ストリームは、データ ラインでリンギングとクロストークの問題を引き起こし、回路基板全体の性能に影響を与えるグランド ワイヤ バウンスと電源ノイズの問題も、電源とグランド プレーンで発生します。

高速データ ラインのリンギングとクロストークを解決するには、まず差動信号を使用することをお勧めします。 差動ペアの 1 つのラインはシンク エンドであり、もう 1 つのラインはソース電流を提供するため、誘導効果は基本的に排除できます。 差動ペアを使用してデータを送信すると、電流がローカルに保持されるため、リターン パスの誘導電流によって生成される「バウンス」ノイズを低減するのに役立ちます。 数百 MHz または数 GHz までの RF 周波数の場合、信号理論は、インピーダンスが一致するときに最大信号電力を送信できることを示しています。 伝送線路がうまく一致しない場合、反射が発生します。 信号の一部のみが送信者から受信者に送信され、他の部分は送信者と受信者の間を行き来します。 PCB での差動信号実現の品質は、インピーダンス整合 (およびその他の側面) において大きな役割を果たします。

差動配線設計

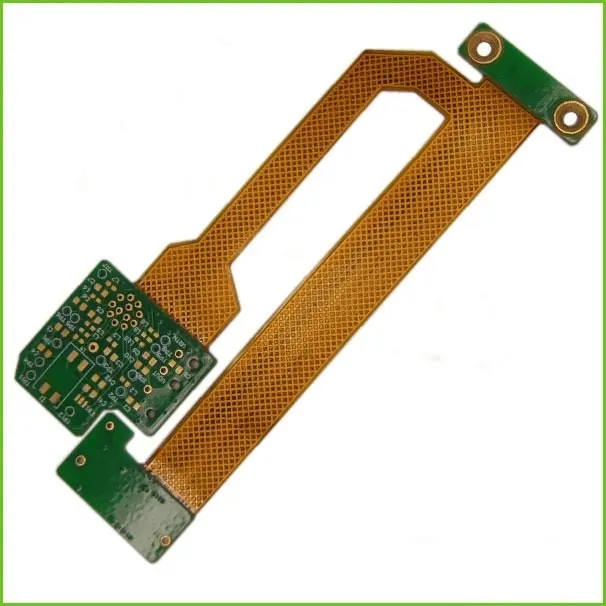

差動配線設計は、インピーダンス制御 PCB の原理に基づいています。 そのモデルは、同軸ケーブルのようなものです。 インピーダンスが制御された PCB では、金属プレーン層をシールド層として使用でき、絶縁体は FR4 ラミネートであり、導体は信号配線ペアです。 FR4 の平均誘電率は 4.2 ~ 4.5 です。 製造誤差は不明であるため、銅線の過度のエッチングにつながり、最終的にインピーダンス誤差につながる可能性があります。 PCB 配線インピーダンスを計算する最も正確な方法は、フィールド解析プログラム (通常は 2 次元、場合によっては 3 次元) を使用することです。これには、有限要素を使用して PCB バッチ全体のマクスウェル方程式を直接解く必要があります。 このソフトウェアは、ワイヤ間隔、ワイヤ幅、ワイヤの厚さ、および絶縁層の高さに従って、EMI の影響を分析できます。

100 Ω の特性インピーダンスは、差動接続ラインの業界標準値になりました。 100 Ω 差動ラインは、同じ長さの 2 つの 50 Ω シングルエンド ラインで構成できます。 2 つのラインは互いに近接しているため、ライン間の電界結合によってラインのディファレンシャル モード インピーダンスが低下します。 100 Ωのインピーダンスを維持するには、配線の幅を少し狭くする必要があります。 その結果、100 Ω 差動ライン ペアの各ラインのコモン モード インピーダンスは、50 ヨーロッパより少し高くなります。

理論的には、配線のサイズと使用される材料によってインピーダンスが決まりますが、ビア、コネクタ、さらにはデバイス パッドでさえ、信号経路にインピーダンスの不連続性が生じます。 通常、これらのものを使用しないことは不可能です。 場合によっては、より合理的なレイアウトと配線のために、PCB 層の数を増やしたり、埋め込み穴などの機能を追加したりする必要があります。 埋め込まれた穴は、PCB 層の一部のみを接続しますが、伝送線路の問題を解決する一方で、基板の製造コストも増加させます。 しかし、まったく選択の余地がない場合もあります。 信号速度がますます速くなり、スペースがますます小さくなり、埋め込み穴などの追加要件が増え始めると、これらは PCB ソリューションのコスト要素になるはずです。

リボン配線を使用する場合、信号は FR-4 素材によって中央でクランプされます。 マイクロストリップラインの場合、導体が空気にさらされています。 空気の誘電率が最も低い (Er=1) ため、最上層は、クロック信号や高周波 SERIAL DESerial (SERDES) 信号などの重要な信号を敷設するのに最適です。 マイクロストリップ ライン配線は、電磁界ラインの一部を吸収することによって電磁干渉 (EMI) を低減する下側のグランド プレーンに結合する必要があります。 ストリップラインでは、すべての電磁界ラインが上下の基準面に結合されるため、EMI が大幅に低減されます。 可能であれば、ワイド エッジ カップリング ストリップライン設計は避ける必要があります。 この構造は、基準面でのカップリング微分ノイズの影響を受けやすくなります。 さらに、制御が難しい PCB バランスの取れた製造も必要です。 一般に、同じレイヤーの行間隔を制御することは比較的簡単です。

デカップリングおよびバイパス コンデンサ

PCB の実際の性能が期待を満たしているかどうかを判断するもう 1 つの重要な側面は、デカップリング コンデンサとバイパス コンデンサを追加して制御する必要があります。 デカップリング コンデンサを追加すると、PCB の電源とグランド プレーン間のインダクタンスが減少し、PCB 上の信号と IC のインピーダンスを制御するのに役立ちます。 バイパス コンデンサは、FPGA にクリーンな電源を供給する (チャージ バンクを提供する) のに役立ちます。 従来のルールでは、デカップリング コンデンサは PCB 配線に便利な場所に配置する必要があり、FPGA の電源ピンの数によってデカップリング コンデンサの数が決まります。 しかし、FPGA の超高速スイッチング速度は、このステレオタイプを完全に打ち破ります。

典型的な FPGA ボード設計では、電源に最も近いコンデンサが負荷電流の変化に対する周波数補償を提供します。 低周波フィルタリングを提供し、電源電圧降下を防ぐために、大きなデカップリング コンデンサを使用する必要があります。 電圧降下は、設計回路の起動時のレギュレータの応答の遅延によるものです。 この大きなコンデンサは通常、低周波応答が良好な電解コンデンサであり、その周波数応答範囲は DC から数百 kHz です。

FPGA 出力が変化するたびに、信号ラインの充電と放電が必要になり、これにはエネルギーが必要です。 バイパスコンデンサの機能は、広い周波数範囲で局所的なエネルギー貯蔵を提供することです。 さらに、高周波トランジェントに高速電流を供給するには、小さな直列インダクタンスを備えた小さな容量が必要です。 応答の遅い大型コンデンサは、高周波コンデンサのエネルギーが消費された後も電流を供給し続けます。

電源バス上の多数の過渡電流は、FPGA デザインの複雑さを増します。 この過渡電流は通常、SSO/SSN に関連しています。 インダクタンスが非常に小さいコンデンサを挿入すると、局所的な高周波エネルギーが提供され、これを使用して電源バス上のスイッチング電流ノイズを除去できます。 高周波電流がデバイスの電源に入るのを防ぐこのデカップリング コンデンサは、FPGA のすぐ近く (1cm 未満) に配置する必要があります。 場合によっては、デバイスのローカル エネルギー ストレージとして多数の小さなコンデンサが並列に接続され、変化する電流需要に迅速に対応できます。

一般に、デカップリング コンデンサの配線は、ビアの垂直方向の距離を含めて、絶対に短くする必要があります。 少しでも増加するとワイヤのインダクタンスが増加し、デカップリング効果が減少します。

その他の技術

信号速度の向上に伴い、回路基板上でデータを簡単に伝送することはますます困難になっています。 PCB の性能をさらに向上させるために、他の技術を使用することができます。

最初の最も明白な方法は、単純なデバイス レイアウトです。 最も重要な接続に対して最短かつ直接的なパスを設計することは常識ですが、この点を過小評価しないでください。 最も単純な戦略が最良の結果を達成できるのに、わざわざボード上の信号を調整する必要はありません。

信号線の幅を考慮する方法はほぼ同じです。 データレートが 622MHz 以上に達すると、信号伝送の表皮効果がより顕著になります。 距離が長い場合、PCB 上の非常に薄い配線 (4 または 5 ミルなど) は、設計されていない減衰を伴うローパス フィルターのように、信号に大きな減衰を引き起こします。 周波数の。 バックプレーンが長いほど、周波数が高くなり、信号線の幅が広くなります。 長さが 20 インチを超えるバックプレーン配線の場合、線幅は 10 または 12 ミルに達する必要があります。

通常、ボード上で最も重要な信号はクロック信号です。 その際、クロックラインが長すぎたり、設計が不十分だったりすると、特に高速化した場合、ジッターとオフセットがダウンストリームに対して増幅されます。 ビアはインピーダンスの変化と反射を増加させるため、複数のレイヤーを使用してクロックを送信することは避け、クロック ラインにビアを配置しないでください。 内層でクロックを配置する必要がある場合は、上層と下層でグランド プレーンを使用して遅延を減らす必要があります。 デザインで FPGA PLL が使用されている場合、電源プレーンのノイズによって PLL ジッターが増加します。 これが重要な場合は、PLL 用に「パワー アイランド」を作成できます。 このアイランドは、金属プレーンのより厚いエッチングを使用して、PLL アナログ電源をデジタル電源から分離することができます。

2Gbps を超えるレートの信号の場合、よりコストの高いソリューションを検討する必要があります。 このような高周波では、バックプレーンの厚さとビアの設計が信号の完全性に大きな影響を与えます。 バック プレートの厚さが 0.200 インチを超えない場合、効果が向上します。 PCB が高速信号の場合、ビアの数を制限するためにレイヤーの数をできるだけ少なくする必要があります。 厚板では、信号層を接続するビアが長く、信号経路上に伝送線路分岐が形成されます。 埋め込み穴はこの問題を解決できますが、製造コストが非常に高くなります。 もう 1 つのオプションは、Rogers 4350、GETEK、または ARLON などの低損失の誘電材料を使用することです。 これらの材料のコストは、FR4 材料と比較してほぼ 2 倍になる場合がありますが、これが唯一の選択肢である場合もあります。

I/O ロケーションの選択肢を提供する FPGA の設計手法は他にもあります。 主要な高速 SERDES 設計では、隣接する I/O ピンを保持する (ただし使用しない) ことで、SERDES I/O を分離できます。 たとえば、SERDES Rx と Tx、VCCRX # と VCCTX #、およびボール位置に関して、3x3 または 5x5 BGA ボール領域を予約できます。 または、可能であれば、I/O グループ全体を SERDES に近づけます。 設計に I/O 制限がない場合、これらのテクノロジはコストを増加させることなく利点をもたらすことができます。

最後に、最適な方法の 1 つは、FPGA メーカーが提供するリファレンス ボードを参照することです。 ほとんどのメーカーはリファレンス ボードのソース レイアウト情報を提供しますが、個人情報の問題により特別な申請が必要になる場合があります。 これらのボードには通常、標準の高速 I/O インターフェイスが含まれています。これは、FPGA メーカーがデバイスの特性評価と認証を行う際にこれらのインターフェイスが必要であるためです。 ただし、これらのボードは通常、さまざまな目的のために設計されており、特定の設計要件に必ずしも一致しないことに注意してください。 ただし、ソリューションを作成するための出発点として機能することはできます

概要

もちろん、この記事ではいくつかの基本的な概念についてのみ説明します。 ここに含まれるトピックは、本全体で説明できます。 重要なのは、PCB レイアウトの設計に多くの時間と労力を費やす前に、目標を見つけることです。 レイアウト設計が完了すると、配線の幅を少し調整するだけでも、再設計には多くの時間と費用がかかります。 PCB レイアウト エンジニアは、実際のニーズを満たすことができる設計を行うことに頼ることはできません。 回路図設計者は、常にガイダンスを提供し、賢明な選択を行い、ソリューションの成功に責任を持つ必要があります。 PCB メーカー、PCB 設計者、PCBA メーカーは、高速 FPGA に基づく PCB 設計技術を紹介します。