回路基板システムの相互接続には、チップから回路基板への相互接続、PCB ボード内の相互接続、および PCB と外部デバイス間の相互接続の 3 つのタイプの相互接続が含まれます。 RF 設計において、相互接続ポイントでの電磁特性は、PCB エンジニアリングが直面する主な問題の 1 つです。 本稿では、上記 3 種類の相互接続設計について、デバイスの設置方法、配線の分離、リード インダクタンスの低減対策など、さまざまな手法を紹介します。

現在、デザインを印刷する頻度はますます高くなっている兆しがあります。 データ転送速度の継続的な成長に伴い、データ伝送に必要な帯域幅により、信号周波数の上限は 1 GHz またはそれ以上に達します。 この高周波信号技術は、ミリ波技術 (30GHz) の範囲をはるかに超えていますが、RF およびローエンドのマイクロ波技術が関与しています。

RF エンジニアリングの設計手法は、より高い周波数で通常発生する強力な電磁界効果に対処できなければなりません。 これらの電磁場は、隣接する信号ラインまたは PCB ラインに信号を誘導し、迷惑なクロストーク (干渉と総ノイズ) を引き起こし、システム パフォーマンスを損なう可能性があります。 バック ロスは主にインピーダンスのミスマッチが原因で発生します。これは、付加的なノイズや干渉と同じ影響を信号に与えます。

リターン ロスが大きいと、次の 2 つの悪影響があります。 2. 入力信号の形状が変化するため、反射信号は基本的に信号品質を低下させます。

デジタル システムは 1 と 0 の信号のみを処理し、非常に優れたフォールト トレランスを備えていますが、高速パルスが上昇するときに生成される高調波により、周波数が高いほど信号が弱くなります。 前方誤り訂正技術はいくつかの悪影響を排除できますが、システム帯域幅の一部が冗長データの送信に使用され、システム パフォーマンスの低下につながります。 より良い解決策は、RF 効果を、シグナル インテグリティを損なうのではなく、シグナル インテグリティに寄与させることです。 デジタル システムの最高周波数 (通常は不十分なデータ ポイント) での合計リターン ロスは - 25dB であることが推奨されます。これは 1.1 の VSWR に相当します。

PCB 設計の目標は、小型化、高速化、低コスト化です。 RF PCB では、高速信号が PCB 設計の小型化を制限することがあります。 現在、クロストークの問題を解決する主な方法は、グランドプレーンを管理し、配線を離し、リードのインダクタンスを減らすことです。 リターン ロスを低減する主な方法は、インピーダンス マッチングです。 この方法には、絶縁材料の効果的な管理と、アクティブな信号線と接地線の分離、特に状態ジャンプのある信号線と接地間の分離が含まれます。

相互接続ポイントは回路チェーンの中で最も弱いリンクであるため、相互接続ポイントでの電磁特性は、RF 設計のエンジニアリング設計が直面する主な問題です。 各連系点を調査し、既存の問題を解決する必要があります。 回路基板システムの相互接続には、チップと回路基板、PCB 基板内の相互接続、および PCB と外部デバイス間の信号入出力が含まれます。

チップと PCB ボード間の相互接続

Pentium IV および多数の I/O 相互接続ポイントを含む高速チップが導入されました。 チップ自体に関して言えば、その性能は信頼できるものであり、処理速度は1GHzに達しています。 最近の GHz Interconnection Workshop で最もエキサイティングだったのは、増え続ける I/O の数と頻度に対処する方法が広く知られていることでした。 チップと PCB 間の相互接続の主な問題は、相互接続密度が高すぎると、PCB 材料の基本構造が相互接続密度の成長を制限する要因になることです。 会議では、革新的なソリューションが提案されました。つまり、チップ内のローカル無線送信機を使用して、隣接する回路基板にデータを送信します。

このスキームが効果的かどうかに関係なく、参加者は非常に明確です。高周波アプリケーションに関しては、IC 設計技術は PCB 設計技術よりもはるかに進んでいます。

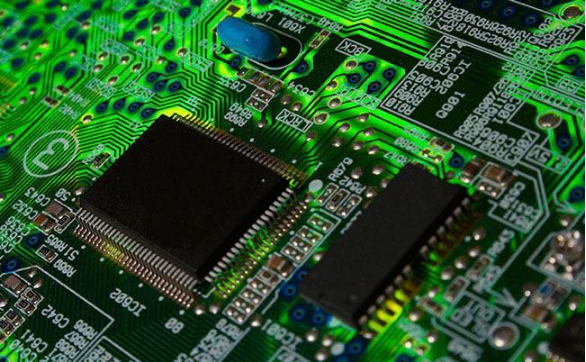

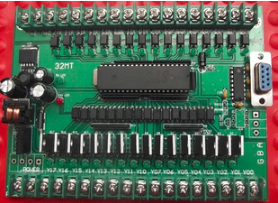

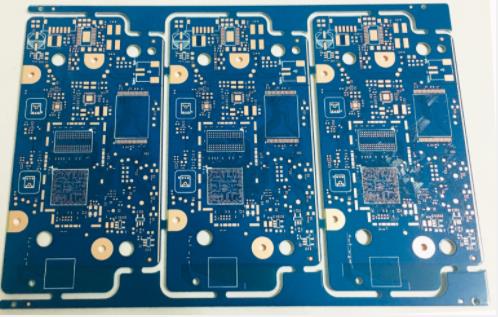

プリント基板

PCB 内部相互接続

高周波 PCB 設計のスキルと方法は次のとおりです。

1.リターンロスを低減するために、伝送ラインのコーナーに45°の角度を採用する必要があります。

2. 絶縁定数が厳密に管理された高性能絶縁基板を使用すること。 この方法は、絶縁材料と隣接する配線との間の電磁界の効果的な管理に役立ちます。

3. 高精度エッチングのための PCB 設計仕様を改善します。 指定された線幅の合計誤差が±0.0007 インチであることを考慮して、配線形状のアンダーカットと断面を管理し、配線側壁の電気めっき条件を指定します。 マイクロ波周波数に関わる表皮効果問題を解決し、これらの仕様を実現するためには、配線(ワイヤー)の形状やコーティング面の総合管理が非常に重要です。

4. リードの突出部にはタップインダクタンスがありますので、リード付部品の使用は避けてください。 高周波環境では、表面実装コンポーネントが推奨されます。

5. 信号ビアの場合、敏感なプレートにビア処理 (pth) プロセスを使用しないでください。このプロセスは、ビアでリード インダクタンスを引き起こすためです。 20 層基板のビアを使用して層 1 ~ 3 を接続すると、リード インダクタンスが層 4 ~ 19 に影響を与える可能性があります。

6. グランドプレーンを豊富に設ける。 成形された穴を使用してこれらの接地層を接続し、回路基板への 3D 電磁界の影響を防止します。

7. 無電解ニッケルめっきまたは金浸漬めっきプロセスを選択し、電気めっきには HASL 法を使用しないものとします。 電気メッキ表面は、高周波電流に対してより優れた表皮効果を提供できます。 さらに、この溶接性の高いコーティングは、必要なリードが少なくて済み、環境汚染の削減に役立ちます。

8. はんだマスクは、はんだペーストの流れを防ぎます。 ただし、厚さの不確実性と絶縁性能の不確実性により、プレート表面全体をはんだ抵抗材料で覆うことは、マイクロストリップ設計の電磁エネルギーに大きな変化をもたらします。 はんだダムは、一般に溶接バリアとして使用されます。

これらの方法に慣れていない場合は、軍用マイクロ波回路基板の設計に携わってきた経験豊富な設計エンジニアに相談できます。 納得できる価格帯も相談できます。 たとえば、銅被覆コプレーナ マイクロストリップ設計は、ストリップライン設計よりも経済的です。 これについて彼らと話し合って、より良い提案を得ることができます。 優秀なエンジニアはコストについて考えるのに慣れていないかもしれませんが、彼らのアドバイスも非常に役に立ちます。 これからは、RF 効果に慣れておらず、RF 効果を扱った経験のない若い技術者を育成するために最善を尽くす必要があります。これは長期的な作業になります。

さらに、コンピューター モデルを改良して RF 効果処理機能を持たせるなど、他の解決策を採用することもできます。

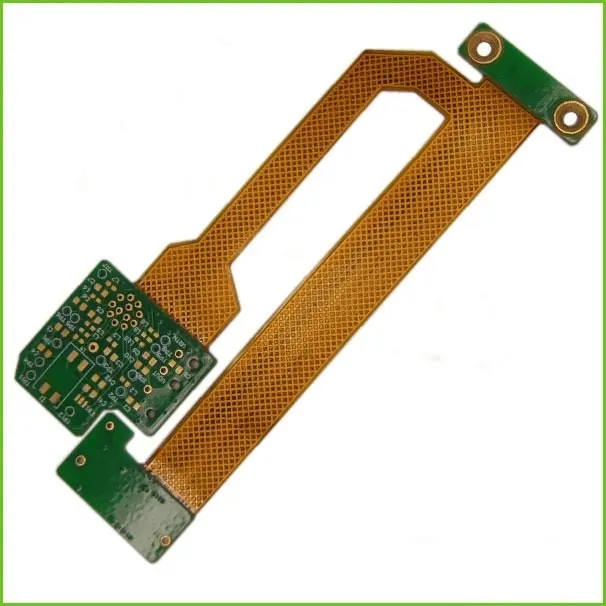

PCB と外部デバイス間の相互接続

これで、ボード上およびさまざまなディスクリート コンポーネントの相互接続に関するすべての信号管理の問題を解決したと考えることができます。 回路基板からリモートデバイスを接続するワイヤへの信号入出力の問題を解決するにはどうすればよいですか? 同軸ケーブル技術の革新者である トロンピーター・エレクトロニクス は、この問題の解決に取り組んでおり、重要な進歩を遂げています。

さらに、PCB で与えられた電磁界を見てください。 この場合、マイクロストリップから同軸ケーブルへの変換を管理します。 同軸ケーブルでは、グランド層は環状にインターレースされ、等間隔に配置されています。 マイクロストリップでは、グランド プレーンはアクティブ ラインの下にあります。 これにより、設計で理解し、予測し、考慮する必要があるいくつかのエッジ効果が導入されます。 もちろん、このミスマッチはリターンロスにもつながります。 ノイズと信号干渉を避けるために、このミスマッチを最小限に抑える必要があります。

回路基板のインピーダンス問題の管理は、無視できる設計上の問題ではありません。 インピーダンスは、回路基板の表層から始まり、はんだ接合部を通ってコネクタに達し、最後に同軸ケーブルで終わります。 インピーダンスは周波数によって変化するため、周波数が高くなるほどインピーダンスの管理が難しくなります。 より高い周波数を使用してブロードバンドで信号を送信するという問題は、設計で直面する主な問題のようです。