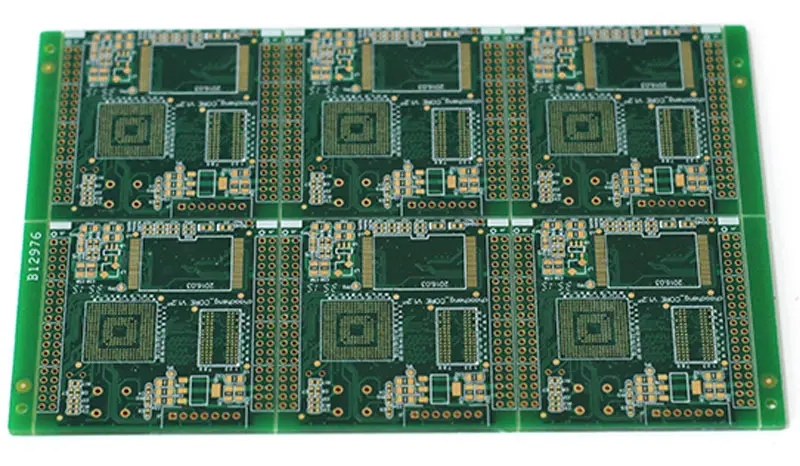

Pcb factory:電子部品内蔵基板の技術動向

はじめに 現在、電子部品やプリント基板は大きく変化しています。 1Cパッケージングは、チップサイズの小型化からメモリ等の立体実装へと発展しています。受動部品は、チップ部品からセラミッククラッド部品へと加速し、受動部品内蔵基板モジュールや1Cパッケージへと発展しています。 それらは、樹脂ベースの基板、特に受動部品および能動部品の基板への移行に向けて動き始めています。 シリコン(Si)チップには、1Cパッケージに適したインサート基板である受動部品チップも集積されており、受動部品内蔵基板の開発が加速しています。 電子部品内蔵基板の技術動向について述べた。

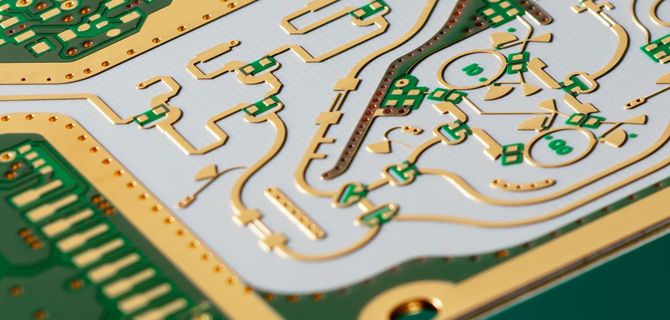

コンポーネントの購入、PCB のカスタマイズ、材料の選択など、電子業界向けのオンライン サプライ チェーン ソリューションを提供し、電子業界の中小企業のお客様の包括的なニーズをワンストップで満たします。

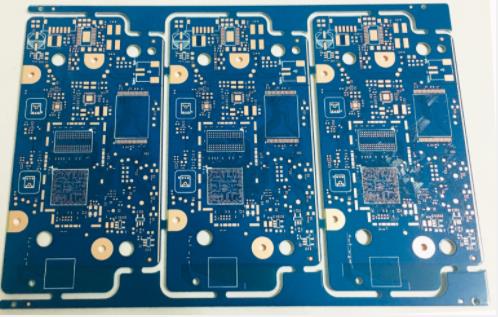

電子部品技術の動向 電子機器の小型化・高性能化・多機能化に伴い、ICパッケージはシングルチップのQFPやTCPから、小型のBGAやCSP、さらに同サイズのウエハレベルCSP(d)へと発展してきました。 ベアチップ。 また、異種ICチップの2次元素子や3次元実装のパッケージ化(MCP、Multi chipPackage)やモジュール化(MCM、Multi ChipModule)の開発も加速しており、ICチップベースのシステムLSIの開発も進んでいます。 非常に活発な。 その後、システムLSI設計の複雑さから、PCB技術に長く携わり、雑誌に多くの論文を発表。

ただし、セラミック基板はもろいため、特殊な小型モジュールやパッケージに限定される大型薄型基板には適していません。 さらに、基板が加熱されると数十パーセントの焼結収縮が発生し、電気的検査や高精度部品の埋め込みが不可能になります。 焼結前後のトリミングができないため、誤差±1%の抵抗を形成することは困難です。 そのため、焼結収縮のばらつき度合いは です。

受動部品集積用 Si 基板の動向 これまで、受動部品集積および組み込み用基板は、セラミックベースの基板が大半を占めていました。 しかし、最近では、半導体技術によってSi基板上に形成されたLRC受動部品の統合受動デバイス(IPD)が導入されました。 これまで、受動部品を集積したSiチップはありませんでしたが、Siチップは、半導体1Cへの組み込みが困難な大容量の受動部品を集積することができます。

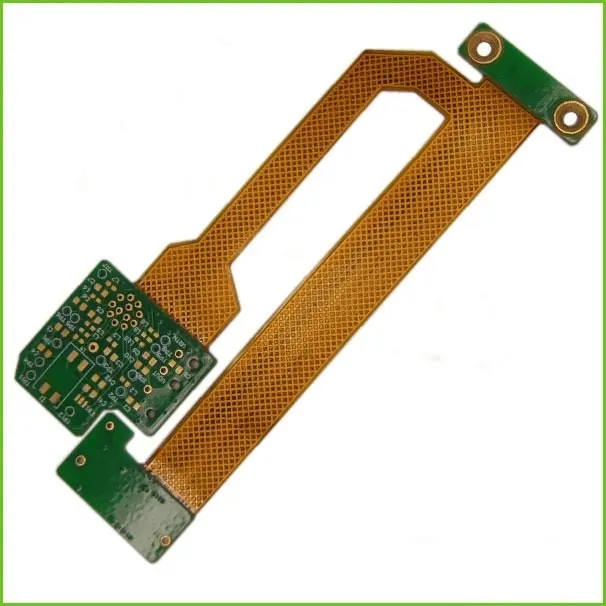

セラミックチップ部品の方向性 マイクロチップデバイスは製造や実装が難しく、単一の部品の実装効率や操作性が非常に悪いため、同じまたは異なる受動部品を持つ2次元または3次元の複合デバイスの数 劇的に増加します。 近年、携帯電話の急速な普及に伴い、1Cを搭載するモジュラー化の流れが加速しています。 しかし、電子機器の高性能化、多機能化、軽量化、小型化にとどまるだけでは不十分です。 数GHzから数十GHz帯の高速・高周波・超小型携帯機の需要が飛躍的に高まっています。 基板と電子部品を別々に製造し、組み合わせて使用する従来の SMT 高密度実装モードでは、性能の向上、小型化、薄型化の要件を満たすことが困難です。 そこで、最近は受動部品や1Cを基板に内蔵することで、部品間の接続長を短くできるほか、配線によるLRCの遅延やノイズ、発熱などを抑えることができます。 実装モードを SMT から SMT に移行すると、電子機器のパフォーマンスが向上し、電子機器の軽量化と小型化が実現されるだけでなく、信頼性が向上し、溶接位置の減少により全体的な設置コストが削減されます。

セラミック複合デバイスに受動部品を埋め込むための基板は、1970年代に開発された低温焼結ガラスセラミック基板にまでさかのぼることができます。 lt: 800t~900tに埋め込むことができる焼結基板は、1980年代半ばに実用化された焼結厚膜抵抗器または厚膜コンデンサです()。 ガラスセラミック基板上にLRCなどを印刷し、積層後に一度焼成する構造です。 ただし、選択範囲が狭いため、一般的には特殊な用途にのみ使用されます。 1980年代後半には、チタン酸バリウム(BaTiQまたはフェライトなどの強電媒体や強磁性体チップに電極を印刷し、積層後に焼結して受動複合素子とする技術((c))。 焼結収縮率や熱膨張係数の異なる生チップを積層・一括同時焼結するため、組成や焼結プロセスに適応性の高い技術が求められ、電子部品メーカーやセラミックスメーカーが力を入れてきました。