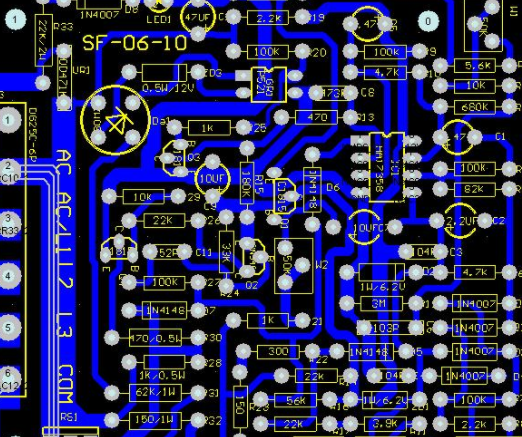

PCBAfaultyはんだ付けの問題を解決する方法

PCBA不良はんだ付けとは何ですか? 表面は溶着しているように見えますが、内部はつながっていない、またはつながっているかもしれないし、つながっていないかもしれない中間の不安定な状態にあることを意味します。 これは最も忌まわしいことです。 問題を見つけるのは難しいです。 それはしばしばコールドはんだと呼ばれます。 溶接不良やスズの不足が原因で、エレメントフットと溶接パッドが外れてしまうものもあります。 その他は、エレメントフットや溶接パッドの酸化や不純物によるもので、肉眼では非常にわかりにくいものです。 一般的には、溶接点の酸化や不純物、溶接温度の悪さ、不適切な方法が原因です。

基本的に、はんだとピンの間に絶縁層があります。 完全には接触しておらず、肉眼ではその状態を確認することはできません。 ただし、それらの電気的特性は導電性がないか、導電性が低く、回路特性に影響を与えます。 PCBA不良のはんだ付けは、一般的な種類の回路障害です。 2種類あります。 1つは、PCBA製造プロセスにおける不適切な製造プロセスによって引き起こされる不安定な状態です。 もう 1 つは、アプライアンスを長期間使用した後、一部の部品の溶接レッグでのはんだ接合部の老化と剥がれが原因で発生します。 コンポーネントは、防湿方法で保管する必要があります。 インライン コンポーネントは、わずかに研磨することができます。 溶接時には、はんだペーストとフラックスを使用できます。 リフローはんだ付け機を使用することをお勧めします。 手はんだ付けは技術的に優れている必要があります。 最初の溶接が良好である限り、一般に誤溶接はありません。 「電化製品を長期間使用すると、一部の部品の溶接脚のはんだ接合部が高温になり、老化や剥離が発生しやすくなります」これは悪い基盤です。

PCBA不良はんだ付けの解決策:

(1) 故障現象からおおよその故障範囲を決定します。 (2) 大型部品や発熱の大きい部品を中心に外観観察。 (3) 拡大鏡で観察します。 (4) 回路基板を引っ張ります。 (5) 疑わしいコンポーネントを手で振って、ピンのはんだ接合部が緩んでいないかどうかを観察します。 PCB会社には独自のPCBボード工場とSMTチップ処理工場があり、PCB製造、部品購入、DIPプラグイン処理、SMTチップ処理、PCBA機能テストのワンストップサービスを提供できます!

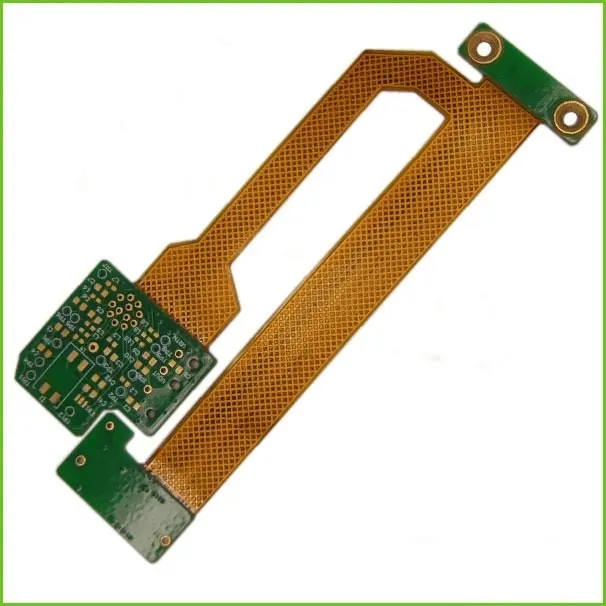

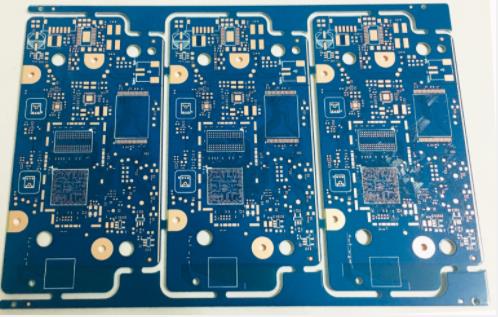

BGA デバイスのレイアウトと配線方法

PCB会社には、平均10年以上の実務経験を持つ専門のPCB設計チームがあり、主流のPCB設計ソフトウェアを巧みに使用できます。 PCB レイアウト設計を持っている友人を歓迎し、相談に来てください! 次に、PCB 設計における BGA デバイスのレイアウトと配線のスキルを紹介します。 ポータブル/小型化およびネットワーク化に向けた電子製品の急速な発展に伴い、電子アセンブリ技術に対するより高い要件が提唱されています。その中で、BGA (Ball Grid Array Package) は実用段階に入っている高密度アセンブリ技術です。 BGA 技術の研究は 1960 年代に始まり、米国の IBM によって最初に採用されました。 しかし、BGA が実際に実用段階に入ったのは 1990 年代初頭のことでした。 以前は QFP パッケージに似た高密度ピン デバイスが普及していたため、細いリードは曲がりやすく、もろく、破損しやすく、リード間のコプラナリティと取り付け精度の要件が非常に高いという、その微細な間隔の制限がありました。 BGA テクノロジーは、新しいデザイン思考モードを採用しています。 丸や円柱の先端をパッケージの下に隠す構造を採用し、リード間隔を広く、リード長を短くしています。 このように、BGA は、ファイン ピッチ デバイスのリード ワイヤの問題によって引き起こされるコプラナリティと反りの欠陥を排除します。 BGA は PCB で一般的に使用されるコンポーネントであり、通常、高周波信号の 80% と特殊な信号がこのタイプのパッケージング フットプリントから引き出されます。 したがって、BGA デバイスの配線をどのように処理するかは、重要な信号に大きな影響を与えます。 BGA デバイスの配線方法は? 通常の BGA デバイスを配線する場合、一般的な手順は次のとおりです。

1. BGAデバイスのボンディングパッド数から必要な基板枚数を決定し、スタック設計を行います。

2. 次に、メイン デバイスの BGA をファン アウトします (つまり、パッドから小さなライン セグメントを引き出し、ラインの端にビアを配置して、ビアが別の層に到達できるようにします)。

3. 次に、ビアからデバイスの端まで配線をエスケープし、すべてのパッドが配線をエスケープするまで、使用可能な層をファンアウトします。 ファンアウトおよびエスケープ中のケーブル接続は、該当するデザイン ルールに従って実行されます。

ファンアウト制御 ファンアウト制御ルール、配線幅 RouTing Width ルール、wiring via method RouTing Via Style ルール、配線層 RouTing Layers ルール、エレクトリカル クリアランス ルールを含む。 ルールが不合理に設定されている場合、たとえば、レイヤーの数が十分でない、無制限の幅が広すぎて外に出ることができない、貫通穴が大きすぎてドリルできない、間隔が安全距離に違反するなど、ファン 失敗します。 ファンアウト操作が応答しない場合は、ルール設定を確認し、適切な変更を加えてください。 ファンアウトは、問題がなくなって初めて成功します。 下の図に示すように。 各レイヤーの配線色が異なります。 [ファン アウト] ダイアログ ボックスでは、ファン アウトおよびエスケープ ルーティングに関連するオプションを制御および定義できます。一部のオプションはブラインド ホールに使用されます (レイヤ ペア間のホールは、スタック マネージャの [レイヤ スタック マネージャ] ダイアログ ボックスで設定できます)。 その他のオプションには、他の 2 つの行と列が内部の行と列と同時にファン アウトされるかどうか、およびネットワークに割り当てられたパッドのみがファン アウトされるかどうかが含まれます。 超小型 BGA (0.4mm 間隔) デバイスの配線方法は? BGA の処理技術は複雑であるため、機能設計に加えて、設計段階で最も重要なことは、PCB メーカーやチップ組立工場とのコミュニケーションです。 メーカーが異なれば、プロセスと機能も異なります。 加工・製造コストについては、プルーフとバッチ生産でも異なります。 したがって、より重要なことは、BGA の設計では、処理コスト、生産の歩留まり率、およびその他の要因も考慮する必要があります。

今日のBGAは燃料節約ランプではありません。 この種の BGA モジュール設計は収益を更新し、最小処理能力のカテゴリに属します。 そのパラメータ特性を見てみましょう。BGA パッドは 0.3mm (12mil)、BGA 中心間隔は 0.4mm (16mil) です。 パッドの X 方向と Y 方向、およびパッドの端から端までは 0.1mm (4mil) です。 パッドとパッドエッジの対角方向は 0.27mm (10.8mil) です。 そこで質問です…! 以前のブログ記事「ルール設定を PCB デザインに適用するにはどうすればよいですか? -- PCB 製造の線幅、線間隔、および穴の直径」を見直して、PCB 処理工場の最も正確な処理能力を紹介します。 さて、主線幅、線間隔、絞り限界処理能力のスクリーンショットは以下の通りです。 最小線幅は 0.1mm (4mil)、最小安全間隔は 0.1mm (4mil)、最小レーザー開口は 0.1mm (4mil) です。 機械的な穴あけは考えていません。レーザー穴は下に置くことができません。