PCBプロセスのチップ実装技術を詳しく解説

1. BGA (ボール グリッド アレイ) は、CPAC (グローバル トップ パッド アレイ キャリア) とも呼ばれます。 面実装パッケージのひとつである球面コンタクト配列。 表示モードではプリント基板の裏面にピンの代わりに球状のバンプを作り、プリント基板の表面にLSIチップを実装し、モールド樹脂やポッティング法で封止します。 バンプ ディスプレイ キャリア (PAC) とも呼ばれます。 ピン数は200ピンを超えることもあり、多ピンLSIに使われるパッケージです。 パッケージ本体もQFP(4サイドピンフラットパック)よりも小型化が可能です。 たとえば、ピン中心距離が 1.5mm の 360 ピン BGA は、わずか 31mm 角です。 中心距離0.5mmの304ピンのQFPは40mm角です。 そしてBGAはQFPのようにピン変形の心配がありません。

このパッケージは、米国のモトローラ社によって開発されました。 最初に携帯電話などで使用され、その後パーソナル コンピュータで普及しました。 当初、BGA ピン (バンプ) の中心間距離は 1.5mm で、ピン数は 225 でした。現在、一部の LSI メーカーは 500 ピン BGA を開発しています。 BGAの課題はリフロー後の外観検査です。 米国モトローラ社ではモールド樹脂で封止したパッケージをOMPAC、ポッティング法で封止したパッケージをGPACと呼んでいます。

2. C - (セラミック) は、セラミック パッケージのマークを示します。 たとえば、CDIP はセラミック DIP を表します。 実務でよく使われるマークです。

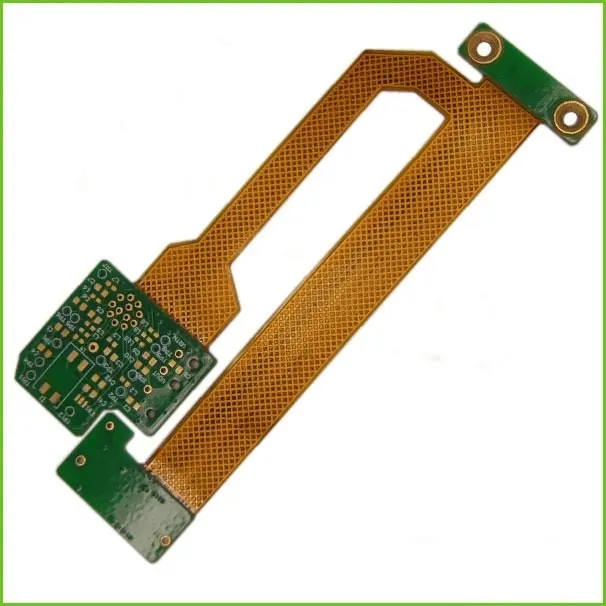

3. COB (Chip On Board) チップパッケージングは、ベアチップ実装技術の 1 つです。 半導体チップを接続し、プリント基板に実装します。 チップと基板間の電気的接続はワイヤステッチで実現し、信頼性を確保するために樹脂で覆います。 COB は最も単純なベア チップ実装技術ですが、そのパッケージ密度は TAB やフリップ チップ ボンディング技術よりはるかに小さくなっています。

4、DIP(デュアルインラインパッケージ)

デュアルインラインパッケージ。 プラグインパッケージの1つで、ピンはパッケージの両側から引き出されており、パッケージ材料はプラスチックとセラミックです。 DIL はヨーロッパの半導体メーカーで広く使用されています。

DIPは最もポピュラーなプラグインパッケージで、その適用範囲は標準ロジックIC、メモリLSI、マイコン回路などです。ピン中心間距離は2.54mm、ピン数は6~64ピンです。 通常15.2mm。 幅が 7.52mm と 10.16mm の一部のパッケージは、それぞれ SK DIP (スキニー デュアル インライン パッケージ) と SL DIP (スリム デュアル インライン パッケージ) ナロー DIP と呼ばれます。 ただし、ほとんどの場合、区別されず、単に DIP と呼ばれます。 さらに、低融点ガラスで封止されたセラミック DIP は Cerdip とも呼ばれます (4.2 を参照)。

4.1 DIC(デュアルインラインセラミックパッケージ)セラミックパッケージ(ガラスシール含む)の別名。

4.2 Cerdip: ECL RAM、DSP (デジタル シグナル プロセッサ) およびその他の回路に使用されるガラス封止セラミック デュアル インライン パッケージ。 ガラス窓付きサーディップは、紫外線消去可能なEPROMやEPROMを内蔵したマイコン回路に使用されています。 ピンの中心間距離は 2.54mm で、ピン数は 8 ~ 42 ピンです。日本では、このパッケージは DIP-G (G はガラスシールを意味します) と呼ばれます。

4.3 SDIP (シュリンク デュアル インライン パッケージ) シュリンク タイプの DIP。 DIPと同じ形状のプラグインパッケージの1つですが、ピン中心距離(1.778mm)はDIP(2.54mm)よりも短くなっています。 ピン数は14本から90本まであります。セラミックスとプラスチックの2種類があります。 別名 SH - DIP (shrink dual in line package)

5、フリップチップ

チップをバックウェルドします。 ベアチップ実装技術の一つとして、LSIチップの電極部に金属バンプを作製し、プリント基板上の電極部に金属バンプを圧接する技術があります。 パッケージのフットプリントは基本的にチップサイズと同じです。 これは、すべてのパッケージング技術の中で最も小さく、最も薄いものです。 しかし、基板の熱膨張係数がLSIチップの熱膨張係数と異なる場合、接合部で反応し、接続の信頼性に影響を与えます。 そのため、LSIチップを補強するために樹脂を使用する必要があり、基本的に熱膨張係数が同じ基板材料を使用する必要があります。

6、FP(フラットパッケージ)

フラットパック。 表面実装パッケージの 1 つ。 QFP または SOP の別名 (QFP および SOP を参照)。 一部の半導体メーカーはこの名前を使用しています。

7、H-(ヒートシンク付)

ラジエーター付きのマークを示します。 たとえば、HSOP はラジエーター付きの SOP の略です。

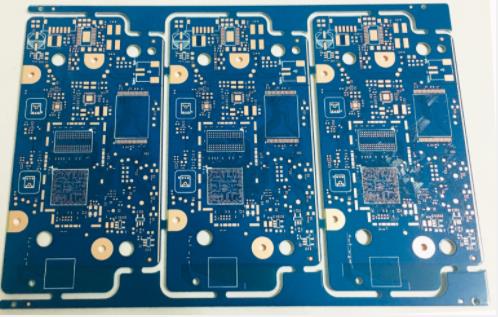

8、MCM(マルチチップモジュール)

マルチチップモジュール。 配線基板上に複数の半導体ベアチップを搭載したパッケージ。 基板材料によると、MCM-L、MCM-C、MCM-D の 3 つのカテゴリに分類できます。 MCM-Lは一般的なガラスエポキシ多層プリント基板を使用した部品です。 配線密度はそれほど高くなく、低コストです。 MCM-Cは、厚膜技術を用いて多層配線を形成し、基板にセラミックス(酸化アルミニウムやガラスセラミックス)を用いた部品です。 これは、多層セラミック基板を使用する厚膜ハイブリッド IC に似ています。 両者の間に大きな違いはありません。 MCM-Lより配線密度が高い。 MCM-Dは、薄膜技術を用いて多層配線を形成し、セラミックス(酸化アルミニウムや窒化アルミニウム)やSi、Alを基板としたモジュールです。 配線の陰謀は 3 つのコンポーネントの中で最も高いですが、コストも高くなります。