ディファレンシャルモード電流とコモンモード電流

放射の生成: 電流は電圧ではなく放射を引き起こし、静電荷は静電場を生成し、定電流は磁場を生成し、時変電流は電場と磁場の両方を生成します。 コモンモード電流とディファレンシャルモード電流はどの回路にも存在します。 差動モード信号は、データまたは有用な信号を伝送します。 同相信号は差動モードの悪影響です。

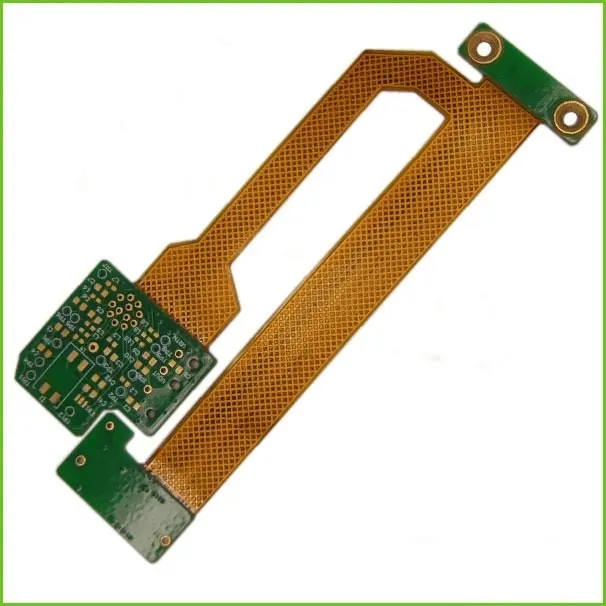

ディファレンシャル モード電流: 大きさが等しく、方向 (位相) が逆です。 PCB 配線の不連続な分布容量、インダクタンス、信号ライン インピーダンス、および信号リターン パスの予期しないパスにより、

ディファレンシャル モード電流はコモン モード電流に変換されます。 コモンモード電流の大きさや方向(位相)は必ずしも同じではありません。

機器の外部干渉は主にコモンモードであり、ディファレンシャルモード干渉も存在しますが、コモンモード干渉強度はディファレンシャルモード強度よりも数桁大きいことがよくあります。 外部干渉は主にコモンモード干渉であり、一般に機器に害を及ぼすことはありません。 ただし、コモンモード干渉がディファレンシャルモード干渉に変換されると、有用な信号はディファレンシャルモード信号であるため、深刻になります。

ディファレンシャル モード電流の磁場は、主にディファレンシャル モード電流によって形成されるループ領域に集中しますが、磁力線はループ領域の外側で互いに打ち消し合います。 コモンモード電流の磁場はループ領域の外側にあり、コモンモード電流によって生成される磁場は同じ方向を持ちます。

PCB の多くの EMC 設計は、上記の理論に従います。

PCB ボード上の干渉を抑える方法は、ディファレンシャル モード信号ループの面積を減らすことです。

高周波ノイズの戻りを減らします (フィルタリング、分離、マッチング)。

コモンモード電圧を下げる(接地設計)。

PCB 設計原則のまとめ

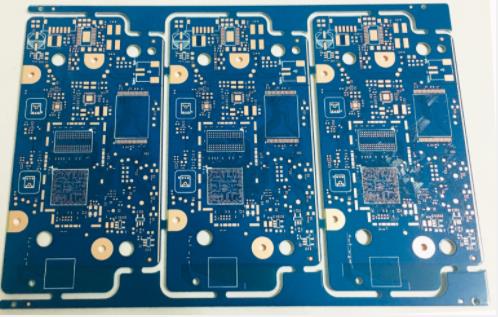

原則 1: PCB クロック周波数が 5MHZ を超えるか、信号の立ち上がり時間が 5ns 未満の場合、通常は多層基板設計を使用する必要があります。

原因: 信号ループの領域は、多層基板設計を使用して適切に制御できます。

原則2:主要な配線層(クロックライン、バス、インターフェース信号ライン、RFライン、リセット信号ライン、チップセレクト信号ライン、各種制御信号ラインが配置される層)は、完全なグランドプレーンに隣接する必要があります 、できれば2つのグランドプレーンの間。

理由: 重要な信号線は、一般的に強い放射線または非常に敏感な信号線です。 グランドプレーンの近くに配線すると、信号回路の面積が減少し、放射強度が減少するか、干渉防止能力が向上します。

原則 3: 単層基板の場合、キー信号線の両側をラップする必要があります。

理由: キー信号の両側が接地されているため、一方では信号ループの面積を減らすことができ、他方では信号線と他の信号線との間のクロストークを防ぐことができます。

原則4:2層基板の場合、キー信号線の投影面は床張りの面積が大きいか、単板と同じように打ち抜かれています。

原因:キー信号がグランドプレーン近くの多層基板と同じ

原則 5: 多層基板では、電源プレーンは隣接するグランド プレーンに対して 5H ~ 20H 縮小する必要があります (H は電源プレーンとグランド プレーンの間の距離です)。

原因: リターン グランド プレーンに対して電源プレーンを縮小すると、エッジ放射の問題を効果的に抑制することができます。

原則 6: 配線層の投影面は、そのリターン プレーン層の領域内にある必要があります。

原因: 配線層がリターン プレーン層の投影領域内にない場合、エッジ放射の問題が発生し、信号ループの面積が増加して、ディファレンシャル モード放射が増加します。

原則 7: 多層ボードでは、ボードの TOP 層と BOTTOM 層に 50MHZ を超える信号線があってはなりません。

理由: 空間への放射を抑制するために、2 つのプレーン層の間で高周波信号を通過させる方がよい。

原則 8: ボード レベルの動作周波数が 50MHz を超えるボードの場合、2 番目の層と最後から 2 番目の層が配線層である場合、TOP 層と BOOTTOM 層は接地銅箔で舗装する必要があります。

理由: 空間への放射を抑制するために、2 つのプレーン層の間で高周波信号を通過させる方がよい。

原則 9: 多層ボードでは、単一ボードの主な動作電源プレーン (最も広く使用されている電源プレーン) は、そのグランド プレーンの近くに配置する必要があります。

原因: グランド プレーンに隣接する電源プレーンは、電源回路のループ領域を効果的に減らすことができます。

原則 10: 単層基板では、電源線に隣接して平行に接地線が必要です。

原因: 電源電流ループの領域を減らします。

原則 11: 2 層基板では、電源線に隣接して平行に接地線が必要です。

原因: 電源電流ループの面積を減らす

原則 12: 階層化された設計では、配線層の隣接設定を避けるようにしてください。 隣接する配線層が避けられない場合は、2 つの配線層の層間隔を適切に広げ、配線層とその信号回路の層間隔を狭くする必要があります。

原因: 隣接する配線層での並列信号配線により、信号のクロストークが発生します。

原則 13: 隣接するプレーン レイヤーは、それらの投影面のオーバーラップを避ける必要があります。

原因: 突起が重なると、層間のカップリング容量により層間ノイズがカップリングされます。

原則 14: PCB レイアウトの設計中は、信号の流れ方向に沿って直線的に配置するという設計原則に完全に従う必要があり、ループの往復は可能な限り回避する必要があります。

原因: 信号の品質に影響を与える信号の直接結合を避けてください。

原則 15: 複数のモジュール回路を同じ PCB に配置する場合、デジタル回路とアナログ回路は、高速回路と低速回路を別々に配置する必要があります。

原因:デジタル回路、アナログ回路、高速回路、低速回路の相互干渉を避ける。

原則 16: 回路基板上に高速、中速、低速の回路が同時に存在する場合、高速および中速の回路をインターフェイスから遠ざける必要があります。

原因: 高周波回路ノイズがインターフェイスを介して外部に放射されるのを防ぎます。

原則 17: エネルギー貯蔵および高周波フィルタ コンデンサは、大きな電流変化を伴うユニット回路またはデバイス (パワー モジュール、ファン、リレーの入出力端子など) の近くに配置する必要があります。

原因: エネルギー蓄積コンデンサの存在により、高電流ループのループ領域が減少する可能性があります。

原則 18: 回路基板の電源入力ポートのフィルタ回路は、インターフェイスの近くに配置する必要があります。

原因: フィルタリングされた回線が再び結合されないようにしてください。

原則 19: PCB ボードでは、インターフェース回路のフィルタリング、保護、および分離デバイスをインターフェースの近くに配置する必要があります。

原因: 保護、フィルタリング、および分離の効果を効果的に達成できます。

原則 20: インターフェースにフィルタリング回路と保護回路の両方がある場合、フィルタリング前の保護の原則に従う必要があります。

原因: 保護回路は、外部の過電圧および過電流抑制のために使用されています。 フィルタ回路の後ろに保護回路を入れると、過電圧、過電流によりフィルタ回路が破損します。

原則 21: レイアウトは、フィルター回路 (フィルター)、絶縁および保護回路の入力ラインと出力ラインが互いに結合されないようにする必要があります。

原因: 上記の回路の入力と出力の配線が互いに結合すると、フィルタリング、絶縁、または保護の効果が弱まります。

原則 22: ボード上のインターフェイスが「クリーン」になるように設計されている場合、フィルターと分離デバイスは「クリーン」と作業場所の間の分離ベルトに配置する必要があります。

原因: 効果を弱めるために、プレーン層を介したフィルタまたは絶縁デバイスの相互結合を避けてください。

原則 23: フィルターと保護装置以外の装置を「きれいな地面」に置かないでください。

理由: 「クリーン」設計は、最小限のインターフェース放射を確保することを目的としており、「クリーン」は外部干渉によって容易に結合されるため、「クリーン」には他の無関係な回路やデバイスがあってはなりません。

原則 24: 水晶、水晶発振器、リレー、スイッチング電源、およびその他の強力な放射デバイスは、シングル ボードのインターフェイス コネクタから少なくとも 1000 ミル離す必要があります。

原因: 干渉は直接外向きに放射するか、出力ケーブルの電流を結合して外向きに放射します。

原則 25: 敏感な回路またはデバイス (リセット回路、WATCHDOG 回路など) は、ボードの端、特にボード インターフェイスの端から少なくとも 1000 ミル離す必要があります。

原因: ボード インターフェイスのような場所は、外部干渉 (静電気など) のカップリングの影響を最も受けやすく、リセット回路やウォッチドッグ回路などの敏感な回路は、システムに影響を与える可能性が非常に高くなります。

誤操作。

原則 26: IC フィルタリングに使用されるすべてのフィルタ コンデンサは、チップの電源ピンのできるだけ近くに配置する必要があります。

原因: コンデンサがピンに近づくほど、高周波回路の面積が小さくなるため、放射が小さくなります。

原則 27: 開始端で直列に接続された整合抵抗は、その信号出力端の近くに配置する必要があります。

原因: 当初の直列整合抵抗の設計目的は、チップ出力端の出力インピーダンスと直列抵抗のインピーダンスの和を配線の特性インピーダンスと等しくすることです。 マッチング抵抗は、上記の式を満たすことができない端に配置されます。

原則 28: PCB 配線には、直角または鋭角の配線があってはなりません。

原因: 直角配線は不連続なインピーダンスにつながり、信号伝送につながり、リンギングやオーバーシュートを引き起こし、強力な EMI 放射を形成します。

原則29:隣接配線層の層設定は極力避ける。 避けられない場合は、2 つの配線層の配線を互いに垂直にするか、平行配線の長さを 1000 ミル未満にするようにしてください。

原因: 平行線間のクロストークを減らします。

原則 30: ボードに内部信号ルーティング層がある場合、クロックおよびその他の重要な信号ラインは内部層でルーティングされます (ルーティング層が優先されます)。

原因:キー信号を内部配線層に敷くことでシールドできます。

原則 31: グランド ワイヤをクロック ワイヤの両側に巻き付けることをお勧めします。グランド ビアは 3000 ミルごとにドリルで開ける必要があります。

原因: 接地線の各ポイントの電位が等しいことを確認してください。

原則 32: クロック、バス、RF ケーブル、およびその他の重要な信号配線と、同じ層のその他の並列配線は、3W の原則を満たす必要があります。

原因: 信号間のクロストークを避けてください。

原則 33: 電流が 1A 以上の電源に使用される表面実装ヒューズ、磁気ビーズ、インダクタ、およびタンタル コンデンサのボンディング パッドは、少なくとも 2 つのビアを介してプレーン層に接続する必要があります。

原因: ビアの等価インピーダンスを下げます。

原則 34: 差動信号線は、同じ層に同じ長さで平行に配置し、同じインピーダンスで、差動線間に他の線を配置しないでください。

理由: 差動ライン ペアのコモン モード インピーダンスが等しいことを確認し、干渉防止機能を向上させます。

原則 35: キー信号配線は、パーティション領域 (ビアとパッドによって引き起こされる基準面のギャップを含む) を横断してはなりません。

原因: パーティションをまたいで配線すると、信号ループの面積が増加します。

原則 36: 信号ラインがリターン プレーン全体でグランドを分割することが避けられない場合、信号クロス スプリットの近くでブリッジ キャパシタンスを使用することをお勧めします。キャパシタンス値は 1nF です。

原因: 信号が分割されると、多くの場合、回路面積が増加します。 信号回路を手動で設定するブリッジ接地方式を採用しています。

原則 37: ボード上のフィルター (フィルター回路) の下に他の無関係な信号を配線してはならない。

原因: 分布容量により、フィルタのフィルタリング効果が弱まります。

原則 38: フィルター (フィルター回路) の入力信号ラインと出力信号ラインは、平行または交差してはなりません。

原因: フィルタリングの前後にノイズが直接結合しないようにしてください。

原則 39: キー信号線と基準面の端との間の距離は ≥ 3H です (H は基準面からの線の高さです)。

原因: エッジ放射効果を抑制します。

原則 40: 金属シェルの接地要素については、その投影領域の最上層を接地銅シートで舗装する必要があります。

原因: 金属シェルと接地銅シート間の分布容量は、外部放射を抑制し、イミュニティを向上させるために使用されます。

原則 41: 単層基板または 2 層基板では、配線時に「ループ面積の最小化」設計に注意する必要があります。

原因: ループ面積が小さいほど、ループの外部放射が小さくなり、干渉防止能力が強くなります。