基板上でのクロック設計上の注意点は、主に3つの側面から考えられます。

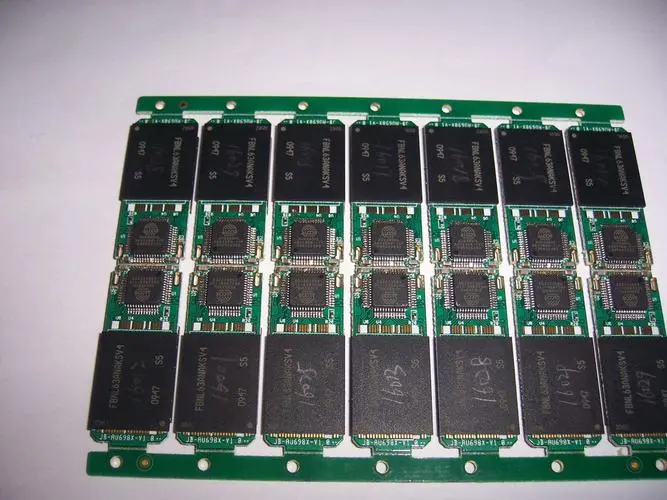

1. PCB レイアウト

1) クロック クリスタルおよび関連する回路は、PCB の中央に配置し、I/O インターフェースの近くではなく、適切な層を持たなければなりません。 クロック生成回路は、サブカードやサブボードにすることはできず、別のクロックボードやベアリングボードに作る必要があります。

2) PCB のクロック回路領域には、クロック回路に関連する PCB デバイスのみを配置し、その他の回路は配置しないこと。 水晶振動子の近くまたは下には、他の信号線を配置しないでください。 グランドプレーンは、クロック生成回路と水晶振動子の下で使用されます。 他の信号がプレーンを通過すると、イメージ プレーンの機能に違反します。 信号がグランド プレーンを通過する場合、小さなグランド ループが存在し、グランド プレーンの連続性に影響を与えます。これらのグランド ループは、高周波で問題を引き起こします。

3) クロック水晶およびクロック回路については、シールド対策を講じることができます。

4) 時計の筐体が金属製の場合、水晶振動子の下に銅を敷き詰め、この部分が完全な接地面と良好に電気的に接続されていることを確認します (多孔性接地を介して)。

5) クロック水晶振動子の下にグランドを配置する利点: 水晶発振器内部の回路が RF 電流を生成します。 水晶が金属シェルでカプセル化されている場合、DC 電源ピンは水晶内部の DC 電圧リファレンスと RF 電流ループ リファレンスの基礎となり、シェルからの RF 放射によって生成された過渡電流はグランド プレーンを通して放出されます。 つまり、金属シェルはシングル エンド アンテナであり、RF 電流のグランドへの放射結合効果としては、最も近いイメージ層とグランド層の 2 層以上で十分な場合があります。 クリスタルの下の床も放熱に優れています。

6) 水晶の下に配置されたクロック回路とグランドはイメージ プレーンを提供します。これにより、関連する水晶とクロック回路で生成されるコモン モード電流が減少し、無線周波数放射が減少します。 グラウンド・プレーンは、ディファレンシャル・モードの無線周波数電流に対する吸収効果もあります。 このプレーンは、複数のポイントを介して完全なグランド プレーンに接続する必要があり、低インピーダンスを提供できる複数のビアが必要です。 このグラウンド プレーンの効果を高めるには、クロック生成回路をこのグラウンド プレーンの近くに配置する必要があります。

7) SMT パッケージの水晶振動子は、金属シェルの水晶振動子よりも RF エネルギー放射が多くなります。ほとんどの表面実装水晶振動子はプラスチック パッケージであるため、水晶振動子内の RF 電流は空間に放射され、他のデバイスに結合されます。

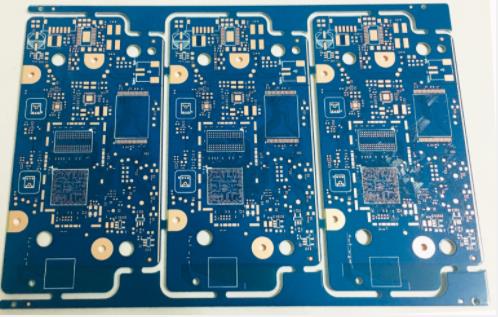

2. 特別な状況と結果

1) 共有クロック配線

高速な立ち上がりエッジ信号とクロック信号の場合、ラジアル トポロジー接続は、単一の共通駆動源を使用するネットワークのシリアル接続よりも優れています。 各経路は特性インピーダンスに応じた終端処理を施して配線してください。

2) クロック伝送ラインの要件と PCB のレイヤリング

クロック ルーティングの原則: クロック ルーティング レイヤーの隣に完全なイメージ プレーン レイヤーを配置して、ルーティングの長さを短縮し、インピーダンス制御を実行します。 不適切なクロス レイヤ ルーティングとインピーダンスの不一致は、次の結果をもたらします。

ワイヤにビアやジャンプを使用すると、イメージ ループが不完全になります。

信号の変化に伴い、画面上の PCB デバイスの信号ピンの電圧が変化することによって発生するサージ電圧。

配線で 3W の原理を考慮しないと、異なるクロック信号がクロストークを引き起こします。

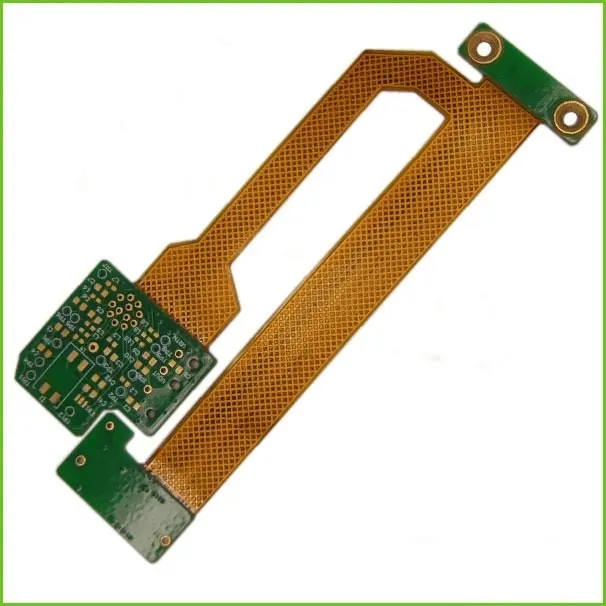

3. 基板配線

1) クロックラインは、多層 PCB 基板の内層にある必要があります。 そして、ストリップラインに従う必要があります。 外層を歩きたい場合は、マイクロストリップラインしか使えません。

2) 内層を歩くことで、イメージ プレーンの完全性を確保できます。 低インピーダンスの RF 伝送経路を提供し、磁束を生成してソース伝送ラインの磁束を相殺することができます。 ソースがリターン パスに近いほど、消磁効果が高くなります。 強化された消磁機能により、高密度 PCB の完全な平面イメージ層ごとに 6 ~ 8dB の抑制を提供できます。

3) クロック クロス多層 PCB ボードの利点: 1 つまたは複数の層を完全な電源とグランド プレーンに特別に使用でき、優れたデカップリング システムに設計でき、グランド ループの面積を縮小し、ディファレンシャル モード放射を低減できます。 、EMI の低減、信号と電源のリターン パスのインピーダンス レベルの低減、ルート全体のインピーダンスの一貫性の維持、隣接するルート間のクロストークの低減など。