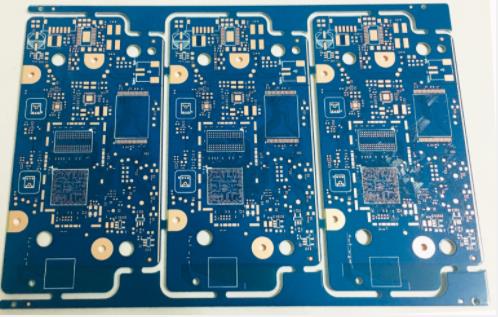

電源システム (PDS) の解析と設計は、高速回路設計の分野、特にコンピューター、半導体、通信、ネットワーク、民生用 PCB 業界でますます重要になっています。 VLSI 技術の必然的なさらなる縮小により、集積回路の電源電圧は低下し続けます。 ますます多くのメーカーが 130nm テクノロジーから 90nm テクノロジーに切り替えるにつれて、電源電圧が 1.2V またはそれ以下に低下し、電流も大幅に増加すると予測できます。 DC IR電圧降下からAC動的電圧変動制御まで、許容ノイズ範囲はますます小さくなり、電源システムの設計に大きな課題をもたらしています。

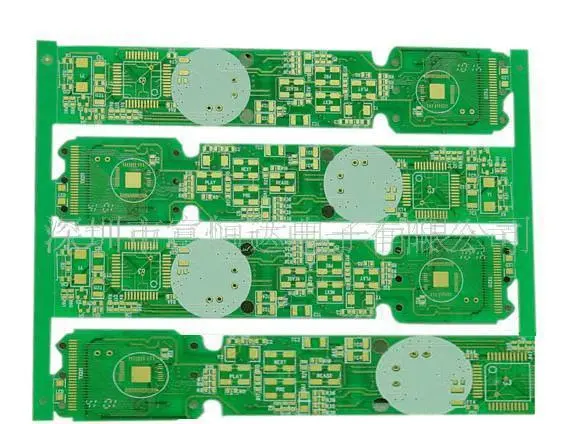

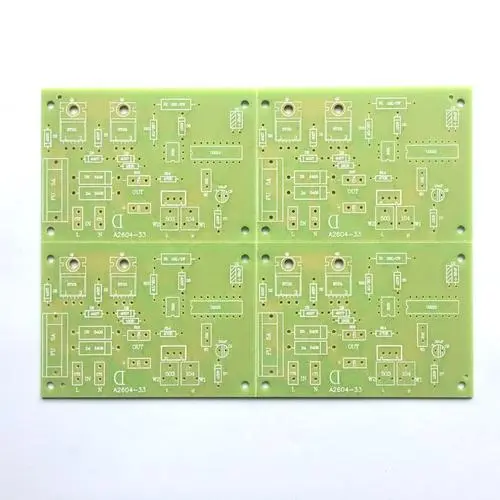

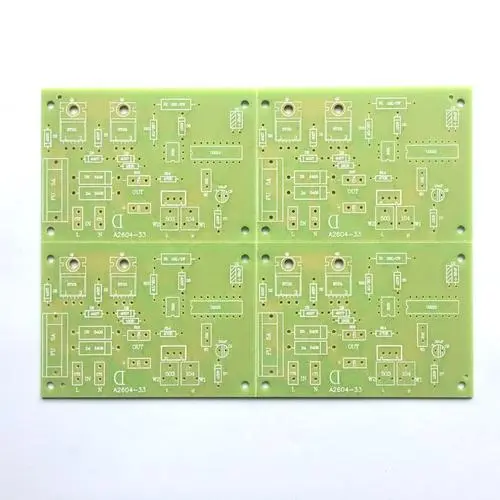

パワー基板設計

AC 解析において、電源とグランド間の入力インピーダンスは、電源システムの特性を測定するための重要な測定値です。 この観測値の決定は、DC 解析における IR 電圧降下の計算になります。 DC 解析でも AC 解析でも、電源システムの特性に影響を与える要因は、PCB の積層、電源基板プレーンの形状、部品のレイアウト、ビアとピンの配置などです。

電源とグランド間の入力インピーダンスの概念は、上記の要因のシミュレーションと解析に適用できます。 たとえば、電源グランド入力インピーダンスの非常に幅広いアプリケーションは、オンボード カップリング コンデンサの配置を評価することです。 基板上に一定数のデカップリング コンデンサを配置することで、回路基板の固有共振を抑えることができるため、ノイズの発生が減少するとともに、回路基板のエッジ放射が減少し、電磁適合性の問題が緩和されます。 電源システムの信頼性と劣化したシステムの製造コストを改善するために、システム PCB 設計エンジニアは、デカップリング コンデンサを備えたシステムの PCB レイアウトを経済的かつ効果的に選択する方法を検討する必要があります。

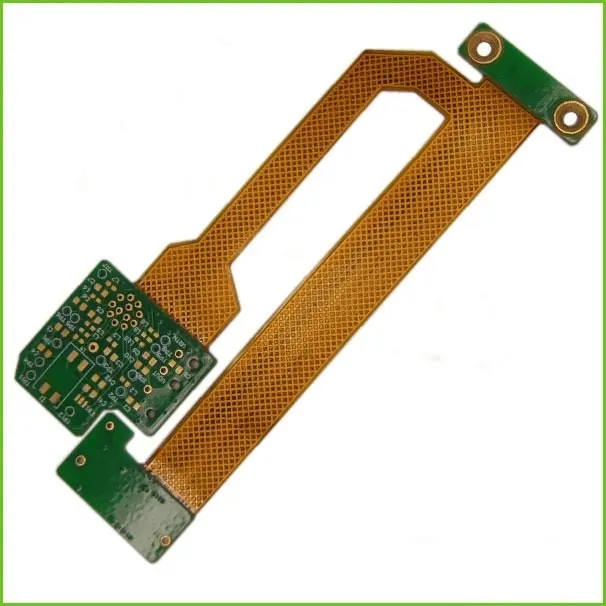

高速回路システムの電源システムは、一般に、チップ、集積回路パッケージ構造、PCB の 3 つの物理サブシステムに分けることができます。 チップ上のパワーグリッドは、交互に配置された数層の金属層で構成されています。 金属の各層は、X または Y 方向の金属ストリップの電源グリッドまたは接地グリッドで構成されます。 ビアは、異なる層の金属ストリップを接続します。

一部の高性能チップでは、コアと IO の両方の電源が多くのデカップリング ユニットと統合されています。 集積回路のパッケージ構造は、複雑な形状の複数の層を持つ縮小された電源またはグランド プレーンのようなものです。 パッケージ構造の上面には、通常、デカップリング コンデンサの実装位置が確保されています。 PCB には通常、大面積の連続した電源とグランド プレーン、いくつかの大小のディスクリート デカップリング コンデンサ コンポーネント、および電力整流器モジュール (VRM) が含まれます。 ボンディング ライン、C4 バンプ、はんだボールがチップ、パッケージ、PCB を接続します。 電源システム全体が、統合された PCB デバイスに通常の範囲内の安定した電圧を提供することを保証する必要があります。 ただし、スイッチング電流と電源システムの寄生高周波効果により、常に電圧ノイズが発生します。