外部 SDRAM を使用する STM32 アプリケーションの一部の顧客は、EMC テスト中に SDRAM 信号が原因で、製品の放射干渉が標準を超えたと報告しています。 端子 PCB 製品の放射干渉をシールドするために筐体を使用できない場合、そのような問題は多くの場合、SDRAM 信号の PCB 設計を変更することによって解決する必要があります。

参考までに、SDRAM の PCB アプリケーション設計における放射干渉の問題を改善する方法の概要を以下に示します。

設計におけるSDRAMの放射線障害対策

SDRAM は高い周波数で動作し、立ち上がりエッジと立ち下がりエッジが急峻です。 そのため、PCB 設計では信号の引き回しを高速信号伝送ラインとして処理する必要があります。 一般に、次の基本原則に注意する必要があります。

1. SDRAM シグナル インテグリティを維持する

SDRAM 信号の歪みは、信号の放射スペクトルをさらに広げ、より深刻な放射の問題を引き起こします。 したがって、PCB 設計を外部委託する場合は、SDRAM 信号の完全性設計に注意を払う必要があります。

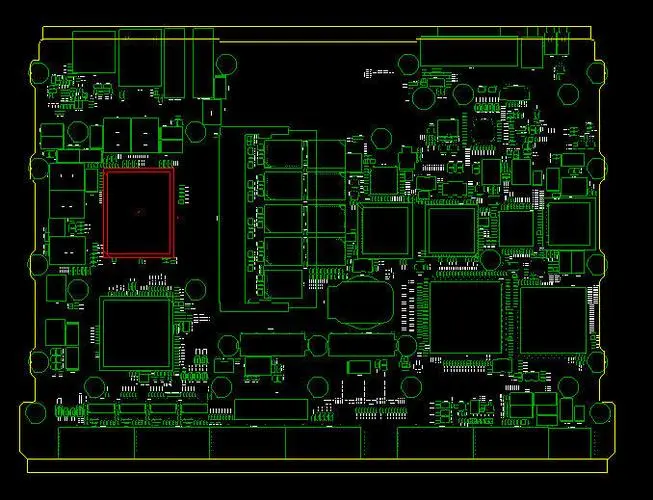

SDRAM 信号の特性インピーダンスを 50 Ω に制御し、SDRAM バス上のビアの使用を最小限に抑え、インピーダンスの連続性を維持し、インピーダンスの不連続性による信号の反射を減らすために、4 層以上の基板を使用することをお勧めします。

SDRAM 信号の配線間隔は 3W の原則に従い、2 つの配線中心間の間隔は可能な限り線幅の 3 倍以上に保つ必要があります。これにより、信号間の干渉による信号の歪みを減らすことができます。

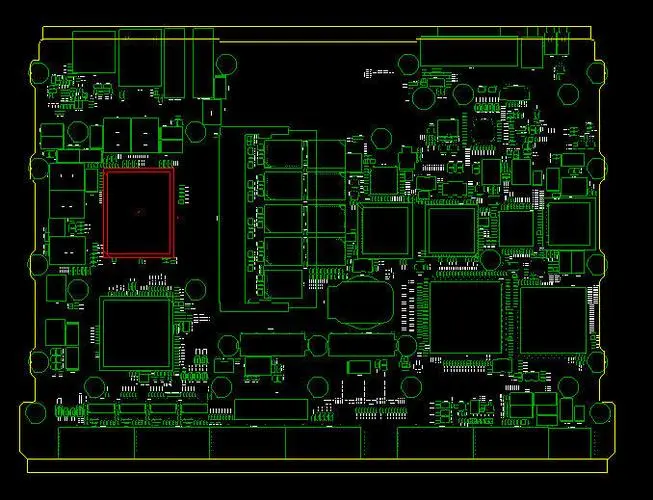

SDRAM を MCU にできるだけ近づけ、MCU から SDRAM への信号配線の長さを短くします (通常は 120mm 以下)。

2. SDRAM 信号のリターン パスを最短に保つ

多層 PCB の場合、高速信号のリターン パスは、基準面へのルーティングの投影です。 PCB 設計では、基準面の完全性と連続性を維持することに注意を払う必要があります。 信号層の変更や電源層の分割により信号の帰路が遮断された場合、階層変更容量/階層変更グランドビアや電源プレーンのジャンパー容量を追加することで、SDRAM信号の最短帰路を確保する必要があります。

3. SDRAM 信号 (特にクロック信号) を PCB の内層に配置します。

SDRAM 信号の中で最も放射レベルが強いクロック信号は、PCB の内層に配置し、外側の銅箔でシールドすることで低減できます。

STM32 の FMC インターフェイスは、SDRAM と FLASH を同時に接続するように設計されています。 SDRAM と FLASH は一部の MCU ピンを共有しているため、それらの複雑なルーティング トポロジにより、SDRAM 信号の放射干渉がさらに強化されます。 SDRAM と FLASH の配線はできる限り PCB の内層に配置し、同時にこれらの信号を PCB の外層でシールドすることをお勧めします。

4. SDRAM 配線領域を他の信号/ケーブルからできるだけ離してください。

結合された SDRAM 放射信号を送信するためのアンテナとして、他の長いルーティング ラインまたはケーブルを使用できるため、それらは PCB 内の SDRAM 信号から離れた領域に配置する必要があります。 必要に応じて、磁気ビーズまたはフィルターをこれらのルーティング ラインまたはケーブルの接続端に配置して、SDRAM 放射信号を減衰させることができます。